fpga仿真不太对 verilog

整数平方根 输入4位二进制整数。

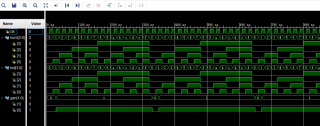

实测正常 但是仿真不正确。

module project_51(

input clk, //时钟信号

input [3:0]num,//输入4位二进制数

output [3:0]led, //输出4位二进制数

output [1:0]gen //输出整数平方根

);

reg [3:0]lastnum;

reg [1:0]sqrt=00;

assign led = num; //输出4位二进制数

assign gen = sqrt;

always @(posedge clk) //计算平方根

begin

if (num != lastnum) sqrt=00;

if ((sqrt+1)**2 <= num) sqrt = sqrt + 2'b01;

lastnum = num;

end

endmodule

仿真文件

module sim_project_51;

reg clk;

reg [3:0]num;

wire [3:0]led;

wire [1:0]gen;

project_51 uut(clk,num,led,gen);

initial begin

clk=0;

num=0000;

end

always #10 clk=~clk;

always #20 num=num+1;

endmodule

感觉仿真中always那块没有循环....(刚开始学,不太会)

- 你这相当于一个周期循环一次,而你的tb给的num+1是每个周期+1,这样还没来得及循环,num就变了,自然always没循环起来

- 楼上将你的num的时间拖得足够长,这样always块自然就跑起来了,有循环的过程

- 如果想一个周期出结果,建议直接用for循环;如果想pipeline的出结果,建议给一个done的信号,判断是否循环完毕;否则为了保证4bit的num能足够时间实现算法,最少最少每个num保持16+个周期

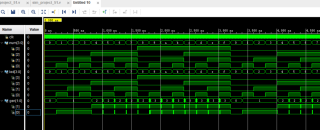

我把仿真文件里面改动了一下

always #5 clk=~clk;

always #200 num=num+1;

大致正确了,但还是有点毛病...