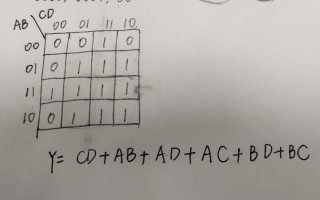

有关卡诺图化简的电路设计问题

设计一个逻辑电路,检验一个四位二进制数是否至少含有两个1,含有两个及以上个1,则输出1,否则输出0

请问以下卡诺图化简结果正确吗?

可以使用多路逻辑门实现对四位二进制数进行判断,具体设计如下:

对于每一位的输入信号,使用一个 2-输入与门(AND Gate)和一个 1-输入反相器(NOT Gate)来实现检查该位是否为 1 的功能,若为 1 则输出 0,否则输出 1。

将四个 2-输入与门的输出信号相连,用一个 4-输入或门(OR Gate)来判断是否至少有两位是 1。

最后将 4-输入或门的输出信号通过一个 1-输入反相器输出即可。

电路图如下:

________

| |

---|>1 |

| |________|

|

| ________

---|>1 |

| |________|

|

_______|________

| | |

---|>1 |>1 |

|________|________|

|

_______|________

| | |

---|>1 |>1 |

|________|________|

|

_______|________

| | |

---|>1 |>1 |

|________|________|

|

_______|_____

| | |

---|>2 |>1 |

|________|_____|

|

_______|

| |

---|>1 |

|_______|

|

|

---

-

其中,“>1”表示一个 2-输入与门,“>2”表示一个 4-输入或门,“>1”后面的符号表示一个 1-输入反相器。在这个电路中,每个 2-输入与门的输入连接到一个输入位,每个 1-输入反相器的输入都连接到对应的 2-输入与门的输出,每个 2-输入与门的输出都连接到 4-输入或门的一个输入,最后的 4-输入或门的输出经过一个 1-输入反相器输出最终结果。