隔离电容耐压该如何选择

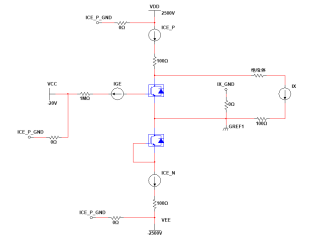

1.试验电路如图所示, 试验要求为测试IGBT模块的反偏及栅偏及绝缘材料漏电流。检测方式为串联采样电阻,通过采集该电阻分压值换算电流。共有三组电源,其中两组高压电源为接地开关电源(直流GND与交流地PE直连),另外一组低压电源为浮地电源。由于四组电源的采样参考地均不相同,故采用隔离方式。电源隔离采用AC-DC隔离电源(隔离等级4kV), MCU与ADC之间使用隔离芯片(隔离等级5kV)。

2.问题如下:现发现模拟信号受到隔离电源影响,采样值有一定程度跳动。目前处理方法是在MCU的参考地和任一模拟参考地之间加一组50nF电容(由2个100nF/2kV串联),可消除采样值跳动影响。但遇到耐压问题,实测加电容情况下,隔离耐压下降,试验电压加至2kV,MCU被击穿;不加电容情况下,试验电压可加至2.5kV? 请教这个故障原因及解决方案

这个问题的根本原因是电容器的介质击穿。在高压下,电容器的介质会出现击穿现象,导致电容器失去隔离作用,从而影响隔离电源的隔离效果。因此,加电容会导致隔离耐压下降,从而导致MCU被击穿。

解决方案是选择耐压更高的电容器,或者采用其他的隔离方式。例如,可以使用光耦隔离器或者磁隔离器来实现隔离。这些隔离器具有更高的隔离等级,可以有效地避免电容器介质击穿的问题。另外,也可以考虑使用更高的隔离等级的AC-DC隔离电源,以提高整个系统的隔离性能。

您好,我是有问必答小助手,您的问题已经有小伙伴帮您解答,感谢您对有问必答的支持与关注!PS:问答VIP年卡 【限时加赠:IT技术图书免费领】,了解详情>>> https://vip.csdn.net/askvip?utm_source=1146287632