HDLbits疑问之旅鼠问题2

实在不知道我的程序哪里出了错

题目

//temp存储落地后像左走还是右

module top_module(

input clk,

input areset, // Freshly brainwashed Lemmings walk left.

input bump_left,

input bump_right,

input ground,

output walk_left,

output walk_right,

output aaah );

reg[1:0] state,next_state,temp;

parameter left=0,right=1,jump=2;

always @(posedge clk or posedge areset) begin

if(areset) state<=left;

else state<=next_state;

end

always @(*) begin

case (state)

left:begin

if(~ground) begin

next_state<=jump;temp<=left;

end

else if(bump_left) next_state<=right;

else next_state<=left;

end

right:begin

if(~ground) begin

next_state<=jump;temp<=right;

end

else if(bump_right) next_state<=left;

else next_state<=right;

end

jump:begin

if(~ground) next_state<=jump;

else next_state<=temp;

end

endcase

end

always @(posedge clk or posedge areset) begin

if(areset) begin

walk_left= 1;walk_right=0;aaah<=0;

end

else begin

walk_left<= next_state==left;

walk_right<= next_state==right;

aaah<= next_state==jump;

end

end

endmodule

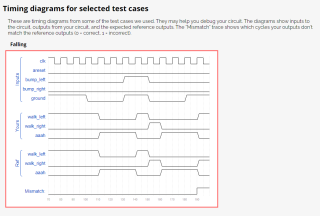

检测:

我大概看了您的代码,我觉得有下列几个问题:

1,always(*)组合逻辑中应使用非阻塞赋值。

2,第三段状态机中,阻塞赋值和非阻塞赋值混用。

3,temp用组合逻辑赋值有点奇怪,希望实现ground结束后保持前态,应该把Latch前态才对。

4,代码中输入到输出,经过了两段FF延时,和题目要求不符。

希望能够帮到您

- 你可以参考下这篇文章:HDLBits刷题网站错误总结(持续更新)

如果你已经解决了该问题, 非常希望你能够分享一下解决方案, 写成博客, 将相关链接放在评论区, 以帮助更多的人 ^-^