大家可以提供一下关于这个的思路嘛,真的看不明白

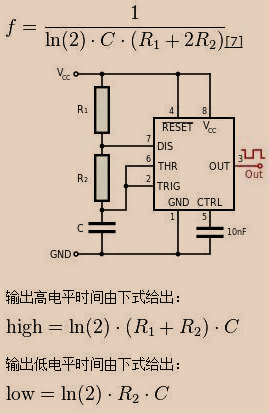

2、时序逻辑电路应用广泛,如银行工作人员员用用点钞机清点钞票的张数,十字路口交通信号装置以倒计时方式显示状态的剩余时间等。在点钞机和交通装置中,都有一-类时序逻辑电路一- -计数器。根据所学知识设计如下电路。

针对你提供的资料,先提供以下参考思路

(1)可以使用74LS160同步计数芯片与与非门结合进行设计,以实现整体置数

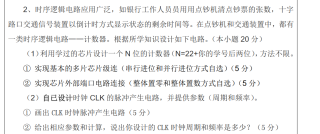

由于你的计数进制为22+学号,所以需要两个74LS160芯片进行级联 ,具体可以参照如下电路

其中U3与非门的输入与你的实际进制有关,需要按照实际情况设计

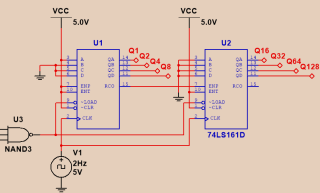

(2)脉冲的生成可以采用555定时器芯片,其具体的电路连接与生成的脉冲频率关系如图所示:

如果感觉有帮助的话请点击采纳~

在设计 N 位计数器时,首先需要确定进位方式,然后根据进位方式设计计数器的芯片连接方式。

如果选择串行进位方式,则需要使用多个计数器芯片连接起来,每个芯片负责计数器的一位,同时还需要使用进位信号将每个芯片的进位信号传递到下一个芯片。

如果选择并行进位方式,则需要使用一个计数器芯片,并将计数器的所有位都连接到芯片的输入端。这样,在每次计数器加 1 时,所有位都会同时进位。

然后还需要考虑如何实现芯片外部端口的电路连接。可以选择使用整体置零或整体置数的方式来控制计数器的初始值。

在设计 CLK 时钟脉冲产生电路时,可以使用一个振荡电路产生脉冲信号,并使用一个时钟芯片来控制振荡电路的频率。设计完成后,可以计算出 CLK 时钟的周期和频率。

注意在设计计数器和时钟脉冲产生电路时,需要考虑电路的稳定性和可靠性。

我用过的74290设计电路,可以参考下https://www.elecfans.com/dianlutu/app/20180126623610.html

提供以下实例讲解参考

【【时序逻辑电路】——计数器】,理论讲解原理,提供理解,链接:https://blog.csdn.net/RL2698853114/article/details/125955394

【时序逻辑设计之计数器】,链接:https://www.cnblogs.com/daxiongjingxiang/p/16461613.html