用verilog HDL语法编写3

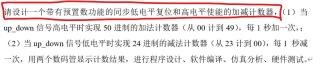

请编写程序,可以给出仿真图,题目如下图,请按题目要求编写,并给出程序。

`timescale 1ns / 1ns

module led_cnt_sim();

reg clk;

reg rst_n;

reg up_down;

reg [7:0] set_dat;

wire[7:0] dat;

initial begin

clk = 0;

up_down = 1;

set_dat = 30;

rst_n = 0;

#40 rst_n = 1;

#4000 set_dat = 40;

rst_n = 0;

#40 rst_n = 1;

#4000 set_dat = 20;

up_down = 0;

rst_n = 0;

#40 rst_n = 1;

#4000 $stop;

end

always #20 clk = ~clk; //50MHz

cnt_xx u1

(

.clk (clk),

.rst_n (rst_n),

.set_dat (set_dat), //预置数

.up_down (up_down),

.dat (dat)

);

endmodule

module cnt_xx //同步计数器,预置

(

input clk,

input rst_n,

input [7:0] set_dat, //预置数

input up_down,

output [7:0] dat

);

reg [7:0] cnt = 0;

assign dat = cnt;

always @(posedge clk )

begin

if( rst_n == 0 ) //rst_n 同步复位

cnt <= set_dat; //rst_n=0 设置预置数

else if(up_down == 1) //0-49加法计数器

begin

if(cnt < 49)

cnt <= cnt + 1;

else

cnt <= 0;

end

else //23-0减法计数器

begin

if(cnt != 0)

cnt <= cnt - 1;

else

cnt <= 23;

end

end

endmodule

你不是已经提问过类似的题目呀,可以参考,自己写一下哇。另外,我看都是同一个人给你解决的,你可以关注他,私信和他交流哇

这几个提问都是你呀