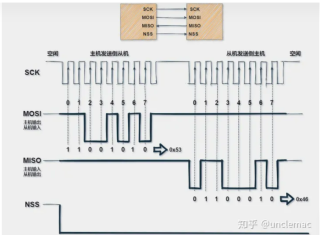

spi接口是全双工传输,但看知乎上一个作者画的波形图中的MOSI和MISO并不是同时传输的

众所周知,spi接口是全双工传输,那为什么我看到一个知乎老哥,画的波形图中的MOSI和MISO并不是同时传输的呢?那我verilog实现功能,modelsim波形仿真时该是选择两个同时传输还是像下面图片那样呢

spi 全双工,这没错

你贴的图也没错

spi 全双工是能工作在半双工的,这没啥奇怪的。

你需要确定你是否要实现 spi 全双工,就需要参考 spi 全双工时序去编写代码

我的理解是,SPI是全双工的,这个图也是全双工可能出现的一种情况。MOSI和MISO互不干涉,所以MOSI和MISO可以有多种相位关系,这是其中一种。可能这个外设需要先接收一个指令,然后才能返回一些数据,所以就是这种时序。

比如这个链接画的时序就是MOSI和MISO同时有数据

https://microcontrollerslab.com/introduction-to-spi-communication-protocol/

至于仿真,自己实现的时候,你的模块也只能控制什么时候发送数据,而不能控制什么时候收到数据。

可以工作在全双工是没错,但实际使用环境下,大多应用都是半双工的,比如很多元件经常都是主机发送一个命令,然后等从机的回答。主机命令发送完成之前,从机无事可做,而从机开始答复的时候,主机除了收数据,基本也没其它事情可做。就像打电话,实际上电话是全双工的,但是两边同时说话,大家都听不清,所以实际情况下大多数是一个人在说另一个人在听,只使用到了半双工。