用verilog HDL语法编写

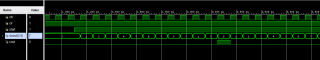

利用always语句设计一个带有同步低电平复位带使能计数功能的十二进制计数器。

时钟信号clk,复位clr,使能端口start,进位cout,计数输出端口daout。

`timescale 1ns/1ns

module testbench_cnt12;

reg clk,clr,start;

wire [3:0] daout;

wire cout;

parameter CLK_PERIOD = 100;

initial

begin

clk = 0;

clr = 0;

start = 0;

#(CLK_PERIOD*4) clr = 1;

#(CLK_PERIOD*7) start = 1;

end

always clk = #(CLK_PERIOD/2) ~clk;

cnt12x ux

(

.clk (clk),

.clr (clr),

.start (start),

.cout (cout),

.daout (daout)

);

endmodule

module cnt12x

(

input clk,clr,start,

output reg cout,

output reg[3:0] daout

);

always@(posedge clk)

begin

if(clr == 0)

begin

cout <= 0;

daout <= 0;

end

else if(start == 1)

begin

if(daout < 12-1)

begin

cout <= 0;

daout <= daout + 1;

end

else

begin

cout <= 1;

daout <= 0;

end

end

end

endmodule