设计脉冲宽度调制器的时候,计数部分结果显示高阻

设计代码

module maichon(clk,clr,duty,period,pwm);

input wire clk;

input wire clr;

input wire [3:0]duty;

input wire [3:0]period;

output reg pwm;

reg [3:0]count;

always@(posedge clk or posedge clr)

if(clr==1)

count<=0;

else if(count==period-1)

count<=0;

else

count=count+1;

always@(*)

if(count<duty)

pwm<=1;

else

pwm<=0;

endmodule

仿真代码

module fangzheng();

reg clk,clr;

reg [3:0]duty;

reg [3:0]period;

wire pwm;

wire [3:0]count;

maichon tt(clk,clr,duty,period,pwm);

initial clk=1;

initial clr=0;

initial duty=4'b0000;

initial period=4'b1111;

always #5 clk=!clk;

always #50 duty=duty+1;

endmodule

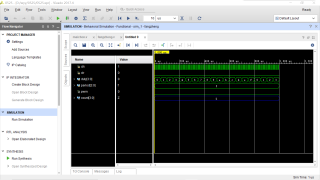

最后的仿真结果里count一直是高阻态是为什么呀

clr 激励信号不对

做为复位信号,clr 不能始终等于0,应该是先等于1几个时钟的时间后在等于0,以后就一直为0就行了。

clr复位信号有问题,没有拉高复位这个动作,导致count就没有初始值,所以就为高阻了。tb文件你可以改成这样:

module fangzheng();

reg clk,clr;

reg [3:0]duty;

reg [3:0]period;

wire pwm;

wire [3:0]count;

maichon tt(clk,clr,duty,period,pwm);

initial clk=1;

initial begin

#0 clr=1;

#10 clr=0;

end

initial duty=4'b0000;

initial period=4'b1111;

always #5 clk=!clk;

always #50 duty=duty+1;

endmodule