在ise14.7中,使用verilog编好的程序生成RTL原理图时,看起来没问题,但是生成的Technology原理图却少了很多东西,好多信号线都直接接地了,有大神可以指点迷津吗?

我在编写一个控制信号的程序时,编译通过后,生成了RTL原理图和Technology原理图,但是看起来好像RTL原理图没什么问题,

但是Technology原理图少了很多东西,比如触发器,很多信号线也直接接地了。

我想问的是,如果程序要烧写到CPLD中,最关键的是要看Technology原理图是吧?

下面是我的一些代码,是我程序写的不对的原因吗?初学者,请见谅~

module process01

(

input I_spi_cs0,

input [3:0] channel0,

input O_rx_done,

output reg opwm0a,

output reg opwm0b,

output reg opwm01,

output reg opwm02,

output reg opwm03,

output reg opwm04,

output reg opwm05,

output reg opwm06,

output reg opwm07,

output reg opwm08,

output reg opwm09,

output reg opwm010,

output reg opwm011

);

always @(posedge O_rx_done )

begin

case(channel0)

4'd0,4'd11,4'd12,4'd13,4'd14,4'd15:

begin

opwm0a <= 1'd0;

opwm0b <= 1'd0;

opwm01 <= 1'd0;

opwm02 <= 1'd0;

opwm03 <= 1'd0;

opwm04 <= 1'd0;

opwm05 <= 1'd0;

opwm06 <= 1'd0;

opwm07 <= 1'd0;

opwm08 <= 1'd0;

opwm09 <= 1'd0;

opwm010 <= 1'd0;

opwm011 <= 1'd0;

end

4'd1:

begin

opwm0b <= 1'd1;

opwm01 <= 1'd1;

opwm02 <= 1'd1;

end

4'd2:

begin

opwm0a <= 1'd1;

opwm02 <= 1'd1;

opwm03 <= 1'd1;

end

4'd3:

begin

opwm0b <= 1'd1;

opwm03 <= 1'd1;

opwm04 <= 1'd1;

end

4'd4:

begin

opwm0a <= 1'd1;

opwm04 <= 1'd1;

opwm05 <= 1'd1;

end

4'd5:

begin

opwm0b <= 1'd1;

opwm05 <= 1'd1;

opwm06 <= 1'd1;

end

4'd6:

begin

opwm0a <= 1'd1;

opwm06 <= 1'd1;

opwm07 <= 1'd1;

end

4'd7:

begin

opwm0b <= 1'd1;

opwm07 <= 1'd1;

opwm08 <= 1'd1;

end

4'd8:

begin

opwm0a <= 1'd1;

opwm08 <= 1'd1;

opwm09 <= 1'd1;

end

4'd9:

begin

opwm0b <= 1'd1;

opwm09 <= 1'd1;

opwm010 <= 1'd1;

end

4'd10:

begin

opwm0a <= 1'd1;

opwm010 <= 1'd1;

opwm011 <= 1'd1;

end

default:

begin

opwm0a <= 1'd0;

opwm0b <= 1'd0;

opwm01 <= 1'd0;

opwm02 <= 1'd0;

opwm03 <= 1'd0;

opwm04 <= 1'd0;

opwm05 <= 1'd0;

opwm06 <= 1'd0;

opwm07 <= 1'd0;

opwm08 <= 1'd0;

opwm09 <= 1'd0;

opwm010 <= 1'd0;

opwm011 <= 1'd0;

end

endcase

end

endmodule

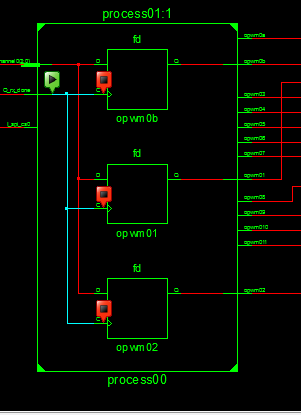

这是生成的技术原理图

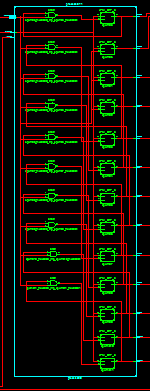

这是生成的RTL原理图