问嵌入式系统时钟树的相关知识?

描述一下时钟树中APB1及APB2如果是8M,系统的时钟及分频系数之间的关系。

【相关推荐】

- 这篇文章讲的很详细,请看:APB总线协议的一些理解

- 除此之外, 这篇博客: APB总线外设接口实现中的 二、APB接口代码分析讲解 部分也许能够解决你的问题, 你可以仔细阅读以下内容或跳转源博客中阅读:

这一章主要讲接口的实现,APB接口比较简单,实现起来也相对easy,这种接口在我个人看来主要用来读写寄存器这种对数据吞吐率没那么高的操作。APB接口的实现也就是要将总线信号转化为更直观的信号,将复杂时序转化为更简单的时序,我将这种转换简称为“翻译”。

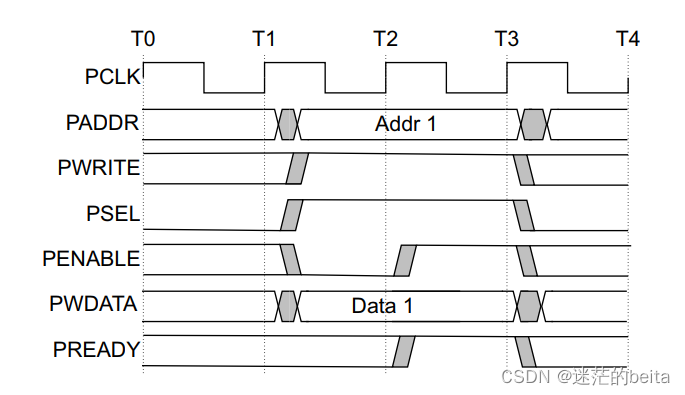

对于写操作,传输过来的地址和控制信号在第一个时钟周期里,数据在第二个周期完成传输。考虑到APB总线在数据未完成传输前地址不会变化,这里可以简化掉地址的一拍寄存,从而节省寄存器资源,节省面积,相关代码如下。assign wr_reg_en = PSEL & PENABLE & PWRITE; assign rd_reg_en = PSEL & (~PENABLE) & (~PWRITE); assign wr_reg_strb = PSTRB; assign rw_reg_addr = PADDR; assign wr_reg_data = PWDATA; assign PREADY = rw_reg_ready; assign PSLVERR = rw_reg_resp; assign PRDATA = rd_reg_data;可以看到这里没有时序逻辑,直接通过组合逻辑即可实现,可见该接口的简洁与轻量级,当PSEL拉高,也就是该外设被选中时,PENABLE为高电平且PWRITE信号为高,也就是在写操作第二个周期里,这是接到寄存器端的写使能信号wr_reg_en为高。读操作同理分析。给到寄存器的strb,addr,data信号都是直接连接传进来的对应总线信号即可。

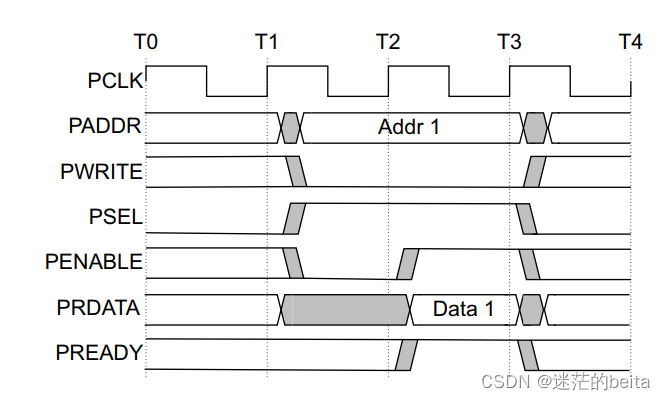

对于APB接口的输出信号:PREADY,PSLVERR,PRDATA,这些直接连接寄存器传来的ready,response,data信号即可,ready往往直接接高电平,也就是always ready的状态,对于寄存器而言数据传输也就只需要一拍,所以直接接高电平。PSLVERR信号往往直接接低电平,因为读写寄存器不会出现什么错误,也可以用来判断地址是否超出,即使出现了错误,主设备一般也很少存在处理错误的操作。PRDATA接寄存器传来的读出数据,这里只是一种实现方式,还可以更严格的按照手册描述的实现,但这样足以满足一般使用要求,同时资源开销接近最少。

有兴趣的可以想想还可以怎么实现,这里就不再讲解第二种实现方式了,给大家留点思考的空间。本专栏会从比较基础的数字ic及FPGA项目开始讲起,逐渐加大难度,大家有什么建议或者想了解的都欢迎和我交流,感兴趣的可以订阅一下。

下期准备讲解AHB总线协议及实现。

如果你已经解决了该问题, 非常希望你能够分享一下解决方案, 写成博客, 将相关链接放在评论区, 以帮助更多的人 ^-^