verilog跨时钟域问题(标签-ar|关键词-main)

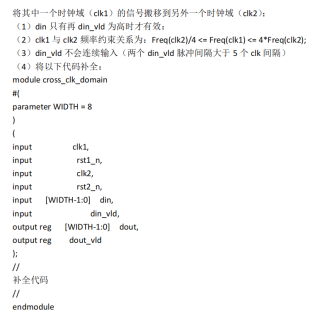

跨时钟域问题解答,今天做笔试题遇到一个跨时钟域问题,以下是题目描述:

最开始想到的是DMUX,但是转念一想不对,请问各位有没有什么实现的思路?

引用 皆我百晓生 小程序回复内容作答:

一个可能的解决方案是使用双钟域同步器(Dual-Clock Synchronizer),将跨时钟域的信号从一个时钟域转换到另一个时钟域。以下是一个可能的实现:

module cross_clock_domain_sync (

input wire clk1,

input wire clk2,

input wire reset,

input wire in_signal,

output reg out_signal

);

reg in_signal1;

always @(posedge clk1 or posedge reset)

if (reset)

in_signal1 <= 1'b0;

else

in_signal1 <= in_signal;

always @(posedge clk2)

out_signal <= in_signal1;

endmodule

在这个例子中,cross_clock_domain_sync模块跨两个时钟域同步信号in_signal。其中一个时钟域由clk1驱动,另一个时钟域由clk2驱动。输入信号通过一个时钟域为clk1的同步器同步到in_signal1中,然后在另一个时钟域为clk2的始终块中,将sinal1赋值给out_signal。

请注意,对于跨时钟域同步器,有一些时序约束和稳定要求需要满足,以确保正确的同步和避免数据冲突。这些约束和要求包括时钟间隔、数据保持时间和时钟相位要求等。在实际设计中,还应该考虑其他方面,如时钟域交叉等特殊情况。在开发中,可能需要进一步调整和优化这个基本解决方案以满足具体的设计要求和约束条件。