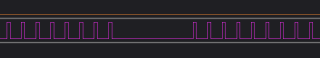

灵动MM32F0130时钟PLL到72Mhz,IO口发送脉冲,低电平会变宽,C和汇编测试都存在这种情况,发生这种情况的原因是什么

灵动MM32F0130时钟PLL到72Mhz,IO口发送脉冲,低电平会变宽,C和汇编测试都存在这种情况,发生这种情况的原因是什么?是时钟不稳定吗?

C程序

while(1)

{

GPIOB->BSRR = GPIO_Pin_3;

GPIOB->BRR = GPIO_Pin_3;

}

汇编程序

AREA ctesr,CODE,READONLY

EXPORT scan_test

GPIOB_BSRR EQU 0X48000410

GPIOB_BRR EQU 0X48000414

scan_test

MOVS R1,#0X01

LDR R2,=GPIOB_BSRR

LDR R3,=GPIOB_BRR

SENDS

STR R1,[R2]

STR R1,[R3]

B SENDS

end

不是时钟问题

是指令执行问题,用软件是无法实现完美的 50% 占空比的方波的

CPU 取指,寻址,跳转等都需要时间,不同的 CPU 时间是不同的,用软件的方法不好控制

时钟不稳定可能是导致低电平变宽的原因之一,但还有其他可能的原因。下面是一些可能导致此问题的原因和建议的解决方法:

时钟不稳定:如果时钟信号不稳定,可能会导致IO口的输出信号出现异常。确保时钟源和时钟设置正确,并进行必要的时钟校准。

GPIO配置错误:检查GPIO端口的配置是否正确。确认引脚模式、速度和推挽/开漏设置是否适当。

延迟问题:由于CPU指令的执行时间不同,可能会导致低电平变宽。尝试在发送脉冲之间添加适当的延迟,以确保IO口具有足够的时间切换到低电平。

上下文切换:如果其他中断或任务正在执行,并且与IO口操作相关,上下文切换可能会导致低电平变宽。在发送脉冲之前,禁用与IO操作相关的中断,并确保在发送脉冲之后重新启用它们。

外部干扰:检查电路板上是否存在任何可能引入干扰的因素,例如电源噪声、信号线附近的干扰源等。使用适当的电源滤波器和信号隔离来减少外部干扰的影响。

硬件故障:检查硬件电路和连接是否正确。可能存在连接问题、元件损坏或其他硬件故障。

请注意,以上是一些建议和常见问题排查步骤。由于缺乏详细的硬件配置和更多背景信息,无法给出具体的解决方案。如果问题持续存在,建议参考芯片厂商提供的技术文档、用户手册或向他们的技术支持寻求进一步的帮助。

- 以下回答由chatgpt基于相关博客总结生成:

由于缺乏问题的具体背景和代码,我无法提供关于配置时钟和PLL的方法,以及发送脉冲的IO口是哪个和使用的编译器版本。需要更多信息才能给出具体的解决方案。

关于低电平变宽的情况如何影响程序,取决于具体的应用场景和代码实现。一般来说,低电平变宽可能会导致信号的传递时间变长,从而影响程序的稳定性和实时性。如果在编写程序时考虑到了这种情况,可以通过合理的设计和调试来提高程序的稳定性和响应速度。