用FPGA做RS485通讯,一帧18位,怎么搞?

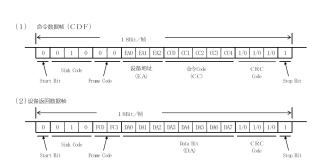

想用 FPGA芯片 EP1C3T144C8 做485通讯,如上图,数据帧18位,请教大师程序怎么做?

以下答案由GPT-3.5大模型与博主波罗歌共同编写:

要实现RS485通信功能,首先需要了解RS485协议和FPGA的串口通信技术。RS485是一种传输速率高、适用范围广的工业通信协议,支持多机通信和远距离传输等特点,适用于工业控制、汽车电子、安防监控等领域。而FPGA芯片是一种可编程芯片,能够实现各种数字逻辑功能和通信接口的设计。

以下是实现RS485通信的步骤:

定义RS485的通信参数:比特率、校验方式、停止位等等。根据通信参数,设置FPGA的串口通信模块,包括设置分频器、时钟信号、波特率等等。

定义数据帧格式:包括起始位、数据位、校验位和停止位。根据数据帧格式,设置FPGA芯片的状态机,实现数据帧的发送和接收功能。

实现发送/接收数据:将需要发送的数据放入FPGA芯片的FIFO缓冲区,然后按照RS485协议进行数据发送。接收数据时,先检测数据是否合法,然后将数据放入FIFO缓冲区。

编写测试程序,测试RS485通信功能是否正常。

下面是一个简单的FPGA实现RS485通信的代码示例。

module rs485 (

input clk,

input rst,

input [17:0] data_in,

output [17:0] data_out,

input tx_enable,

output reg tx_done,

input rx_enable,

output reg rx_done,

output reg dr);

reg [17:0] tx_data;

reg [2:0] tx_state;

reg [2:0] rx_state;

reg [17:0] rx_data;

wire rx = dr;

always @(posedge clk) begin

if (rst) begin

tx_data <= 18'h0000;

tx_state <= 3'h0;

rx_state <= 3'h0;

rx_data <= 18'h0000;

tx_done <= 1'b0;

rx_done <= 1'b0;

end else begin

case (tx_state)

3'h0: begin // idle

if (tx_enable) begin

tx_data <= data_in;

tx_state <= 3'h1;

tx_done <= 1'b0;

end

end

3'h1: begin // start bit

dr <= 1'b0;

tx_state <= 3'h2;

end

3'h2: begin // data bits

dr <= tx_data[0];

tx_data <= {tx_data[16:1], 1'b0};

if (tx_data == 18'h0000) begin

tx_state <= 3'h3;

end

end

3'h3: begin // stop bit

dr <= 1'b1;

tx_state <= 3'h0;

tx_done <= 1'b1;

end

endcase

case (rx_state)

3'h0: begin // idle

if (rx) begin

rx_data <= 18'h0000;

rx_state <= 3'h1;

rx_done <= 1'b0;

end

end

3'h1: begin // start bit

if (!rx) begin

rx_state <= 3'h2;

end

end

3'h2: begin // data bits

rx_data <= {rx_data[16:1], rx};

if (rx_data == 18'h0000) begin

rx_state <= 3'h3;

end

end

3'h3: begin // stop bit

rx_state <= 3'h0;

rx_done <= 1'b1;

end

endcase

end

end

assign data_out = rx_data;

endmodule

这个代码实现了一个简单的RS485通信模块,包括数据发送和接收功能,可以通过修改参数来适配不同的通信需求。

如果我的回答解决了您的问题,请采纳!

要用FPGA芯片EP1C3T144C8做485通讯,你需要先了解FPGA芯片的基础知识,编写VHDL代码,并进行硬件设计与调试。具体可以按照以下步骤来实现:

- 确定RS-485通信的物理接口:连接方式、线路驱动方式、信号电平等。并根据这些参数选择合适的电路方案。

- 在FPGA中设计RS-485通信协议的数据帧格式,包括起始位、数据位、校验位等,以及数据的编解码方式。

- . 编写VHDL代码,对数据进行解码、解帧、处理和编码,并将数据发送到RS-485物理层驱动电路。

- 进行仿真和调试:通过仿真软件对VHDL代码进行仿真,检测是否有错,并进行调试和优化。

- 硬件设计:将FPGA芯片、RS-485转换芯片等外围电路组装在一起,按照设计图进行PCB布线,并进行硬件调试与测试。

使用FPGA进行RS485通信,一帧18位,可以按以下步骤实现:

选择FPGA器件和RS485收发器芯片。常用的FPGA如Xilinx的Spartan系列,RS485收发器可以选择MAX485等。

设计RS485通信接口电路。包括FPGA的GPIO用于发送和接收,RS485收发器等。

设计串行通信协议。如一帧18位,包括1位起始位,8位数据位,1位校验位(可选),1位停止位。速率选择适当,如9600bps。

在FPGA中设计串行通信模块。包括:

(1)发送模块:在FPGA的时钟信号下,按设计的协议格式发送数据。控制RS485收发器芯片发送。

(2)接收模块:检测输入的起始位,然后在时钟信号下按设计的协议格式采样并接收数据位和校验位。检验校验位是否正确(如果有),将接收到的数据在FPGA中缓存或处理。

(3)发送/接收控制:控制RS485发送器和接收器的使能,选择发送或者接收状态。

编写FPGA设计的Verilog或VHDL代码,使用芯片厂商的IDE工具(如Xilinx ISE)进行仿真调试,最后下载到FPGA中验证。

可以在FPGA中集成更复杂的应用,如使用RS485和上位机通信,在FPGA内部处理和控制等。

综上,FPGA使用串行通信协议(如RS485)的关键是在FPGA内部设计好串行发送/接收模块和相应的控制逻辑。外部电路主要用于电平转换。通过稳定的时钟信号,采用合适的通信速率和数据格式,可以很好地实现FPGA和外围设备之间的串行通信。

如有任何不理解的地方或其他问题,也请随时提出。我们可以进一步讨论技术细节,共同学习与提高。