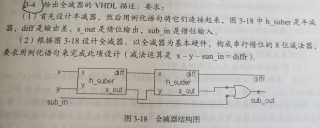

EDA技术全减器的VHDL描述

1.设计半减器,用例化语句将他们连接起来,图以上传。

2.设计全减器,以全减器为基本硬件,构成串行借位的8位减法器,用例化语句来完成设计

以下内容部分参考ChatGPT模型:

半减器的VHDL描述:

library ieee;

use ieee.std_logic_1164.all;

entity half_subtractor is

port (

A : in std_logic;

B : in std_logic;

Diff : out std_logic;

Borrow : out std_logic

);

end half_subtractor;

architecture behavior of half_subtractor is

begin

Diff <= A xor B;

Borrow <= not A and B;

end behavior;

全减器的VHDL描述:

library ieee;

use ieee.std_logic_1164.all;

entity full_subtractor is

port (

A : in std_logic;

B : in std_logic;

Bin : in std_logic;

Diff : out std_logic;

Bout : out std_logic

);

end full_subtractor;

architecture behavior of full_subtractor is

begin

process (A, B, Bin)

begin

Diff <= A xor B xor Bin;

Bout <= (not A and B and Bin) or (A and not B and Bin) or (A and B and not Bin) or (not A and not B and Bin);

end process;

end behavior;

串行借位的8位减法器的VHDL描述:

library ieee;

use ieee.std_logic_1164.all;

entity subtractor is

port (

A : in std_logic_vector(7 downto 0);

B : in std_logic_vector(7 downto 0);

Cin : in std_logic;

Difference : out std_logic_vector(7 downto 0);

Cout : out std_logic

);

end subtractor;

architecture behavior of subtractor is

component full_subtractor is

port (

A : in std_logic;

B : in std_logic;

Bin : in std_logic;

Diff : out std_logic;

Bout : out std_logic

);

end component;

signal D : std_logic_vector(7 downto 0);

signal Bc : std_logic_vector(7 downto 0);

begin

D(0) <= A(0) xor B(0) xor Cin;

Bc(0) <= (not A(0) and B(0) and Cin) or (A(0) and not B(0) and Cin) or (A(0) and B(0) and not Cin) or (not A(0) and not B(0) and Cin);

subtractor_loop : for i in 1 to 7 generate

Fs : full_subtractor port map (A(i), B(i), Bc(i-1), D(i), Bc(i));

end generate;

Difference <= D;

Cout <= Bc(7);

end behavior;

如果我的建议对您有帮助、请点击采纳、祝您生活愉快

- 建议你看下这篇博客👉 :EDA与VHDL题库