Verilog中的状态机问题-->输出到底是什么时候输出?

Verilog中的状态机问题-->输出到底是什么时候输出?

最近刷HDLbits很不理解,状态机究竟是一转换到这个状态立马就要输出(转化到下一个状态很短的时间)还是这个状态要转换之前才输出?

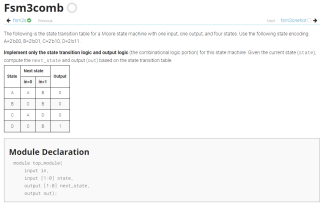

可能表述不是很清楚,还是看图来说(只看图中的表格就可以)。

最后的输出 到底应该是以下的哪一种?

第一种:

always @(*) begin

out<=state==D?1:0;

end

第二种

always @(*) begin

out<=next_state==D?1:0;

end

以下答案引用自GPT-3大模型,请合理使用:

答案:第一种: always @(*) begin

out<=state==D?1:0;

end

因为当当前状态为D时,out才会输出1。

如果我的回答解决了您的问题,请采纳我的回答

该回答引用ChatGPT

在 Verilog 中,状态机的输出通常是在状态转换后立即更新。在您的状态图中,从状态 C 到状态 D 的转换上有一个输出,这意味着一旦状态机进入状态 D,就应该立即产生输出。因此,您应该使用第二种方法:

always @(*) begin

out <= next_state == D ? 1 : 0;

end

在这里,next_state 是状态机下一个状态的值,因此当它等于 D 时,out 将被设置为 1,否则为 0。这种方法保证了在状态转换时立即更新输出。