fpga gtp无时钟信号输出的问题

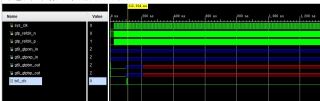

请教一下各位,我照着资料上的方式配置了一个gtp的ip核,start from scratch 基本方式,打开ip例子程序以后,我在gtwizard_0_exdes模块把txusrclk2时钟信号引出来了,仿真的时钟发现txusrclk2一直是0,并没有时钟信号,请问一下大概是什么原因,如下图,只是在100多ns的时候有个峰,别的一直是0

时间有些久,以前也遇到这个问题。有些映像

VIVADO 的 GTP 的仿真非常慢,我记得需要跑 1 小时时间才能看到正确的波形。可能以前的电脑慢些。你耐心多等会吧。

您好,根据您提出的关于fpga gtp无时钟信号输出的问题,为您推荐以下解答思路:

1、检查没有具体的报错信息

2、如果没有具体的报错信息,则一步一步检查您的配置是否有遗漏和错误,包括gtp的配置以及gtwizard_0_exdes的引入等。

3、有一个可能是仿真速度慢的原因,您可以放置一段时间再来看看结果,如果是,说明是时钟速率的问题。

4、如果是时钟速率的问题,那你需要确保通过rtl层次结构将EXAMPLE_SIM_GTRESET_SPEEDUP参数拉到gt_channel级别。确保将EXAMPLE_SIMULATION参数设置为1等等,具体可以参考:https://www.likecs.com/show-204638708.html#sc=400

据我多年的经验来看,出现问题的原因大概有以下几种,望采纳

错误的时钟配置:GTP需要准确的时钟信号来驱动其运行,因此时钟的配置非常重要。如果时钟频率不正确,或者时钟信号的相位和时序不正确,GTP可能无法正常工作。

信号线连接不正确:请确保正确连接了所有必需的信号线,如时钟、数据、复位和控制信号等。如果有任何信号线未正确连接,可能会导致GTP无法正常工作。

信号干扰:GTP非常敏感,因此可能会受到电磁干扰或信号串扰的影响。请确保在设计中采取了适当的干扰抑制措施,并将信号线正确地布线和屏蔽。

电源电压不稳定:GTP需要稳定的电源电压来正常工作。如果电源电压不稳定,可能会导致GTP无法正常工作。

如果在仿真中 txusrclk2 信号始终为 0,则有可能是因为:

1.在仿真过程中没有生成正确的时钟信号。可以检查时钟源是否正确配置,并且是否启用了时钟使能信号。

2.txusrclk2 的时钟源没有正确连接到模块中。在模块中,txusrclk2 应该连接到 GTP 的时钟端口。检查一下模块是否正确连接到 IP 核中。

3.在 IP 核的配置中,时钟参数没有正确配置。可以检查 IP 核的配置是否正确,特别是时钟频率和时钟相位等参数是否正确。

如果您已经排除了上述问题,可以考虑在仿真中添加一些调试输出,以便更好地理解信号的行为。另外,您也可以考虑向 Xilinx 技术支持寻求帮助。

可能是因为仿真的时钟源没有正确配置,或者仿真的时钟源有故障。你可以检查一下仿真的时钟源的配置是否正确,以及仿真的时钟源是否有故障。此外,你还可以检查一下仿真时钟源和txusrclk2之间的连接是否正确

可能存在多种原因导致txusrclk2信号一直是0:

1.GTP的输出引脚与板子上的物理引脚没有正确连接,导致输出信号无法传递到其他电路。

2.GTP的配置文件可能有误,导致GTP没有正确地初始化。可以尝试重新生成GTP的配置文件,并确保正确地加载。

3.时钟信号的频率可能太高,导致仿真工具无法准确地捕获时钟信号。可以尝试降低时钟频率,或使用更高精度的仿真工具。

4.时钟信号的相位可能有误,导致仿真工具无法正确地捕获时钟信号。可以尝试调整时钟信号的相位。

建议检查以上可能的原因,并尝试逐一解决问题。如果仍然无法解决问题,可以考虑咨询FPGA厂商或开发社区的技术支持人员。

从提供的截图来看,txusrclk2 信号一直是低电平,并且仿真中出现了一个短暂的高电平脉冲。这可能有以下几个原因:

1.错误连接:请检查 txusrclk2 信号的源和目标之间的连接是否正确。确保时钟信号已正确连接到模块的输入端口。

2.错误的时钟频率:请确保 txusrclk2 信号的频率与您的设计时钟频率匹配。如果时钟频率不正确,可能会导致时钟信号出现异常。

3.模块配置错误:请确保您已正确配置了 GTP IP 核的参数,并且已为其分配了正确的引脚。确保您的仿真环境正确模拟了所使用的 GTP IP 核。

可以逐一排除上述原因,找出导致时钟信号异常的具体原因。如果仍然无法解决问题,建议参考 Xilinx 官方文档和用户手册,或向 Xilinx 官方技术支持寻求帮助。

GTP(Gigabit Transceiver)是FPGA中的一种高速串行通信接口,它的设计和调试需要一定的经验和技能。在出现时钟信号输出的问题时,可以考虑以下几点:

1 GTP IP核的正确性:首先要检查GTP IP核是否被正确实例化,且与外部的时钟信号和复位信号连接正确。

2 时钟信号的质量:在高速串行通信中,时钟信号的质量对系统性能影响很大。时钟信号的质量包括时钟频率、占空比、抖动、时钟上升/下降时间等。如果时钟信号质量不好,会导致数据传输错误、时序问题等。可以尝试使用示波器或逻辑分析仪对时钟信号进行检测和分析。

3 PCB设计:GTP的高速信号需要考虑信号完整性和阻抗匹配等问题。在PCB设计时需要按照FPGA厂商提供的设计指导进行设计。

4 仿真时钟的设置:在仿真过程中,需要将仿真时钟设置为与实际时钟接近的频率。如果设置的频率过低,时钟上升/下降时间过长,可能会导致仿真结果与实际情况不一致。

针对具体的情况,可以逐一排查以上几点,找出问题所在,并采取相应的措施。

如果对您有帮助,请给与采纳,谢谢。

检查一下是否将正确的时钟信号连接到了GTP的时钟输入