Verilog数据产生器代码疑点

刚开始接触FPGA工作,最近在学习公司老哥写的代码时,遇到了这么个问题。

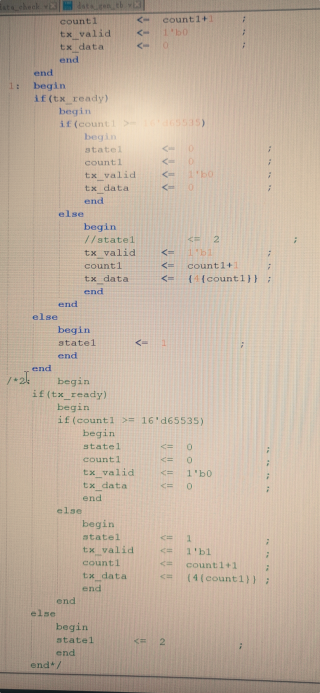

老哥写的完整代码是包括注释部分内容的,我不明白为什么要在两个状态之间跳转着去产生数据,如果将注释部分删掉的话,结果是一模一样的。这样做会对后级产生什么影响吗?还是可以避免什么问题?大家有没有遇到过这样的情况

两部分代码还是不一样的

1:state1 的值在0,2 两个数之间变化

2:state1 的值在0,1,2 三个数之间变化

你说的结果是一模一样,可能是你没有全面测试的原因

这样方式的更改一般是在发现 BUG 时做的临时修改。一般严谨的话,经过全面的代码测试后会删除这些注释。也可能测试并不全面的临时修改。

在老哥写的代码中,在两个状态之间跳转着生成数据,是因为状态机是通过状态的转移来控制系统的行为,这种模式下,一个状态的转移需要依靠当前的 tx_ready 状态。删除不删除都是一样的,注释部分反正不会被执行,有可能是老哥为了区分代码块写的。