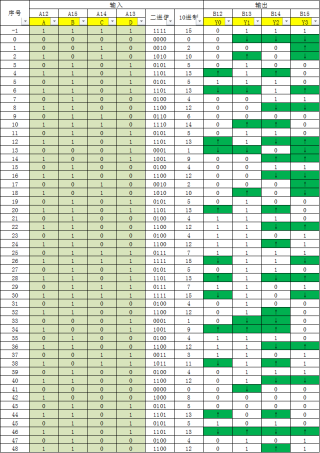

分析波形图对应的逻辑关系

图片所示逻辑波形,四个输入,四个输出,有尝请人分析逻辑关系或做出逻辑电路图&Verilog HDL代码也行,完整波形,此CPLD无时钟输入,完整的资料在网盘,包括波形文件及打开软件

链接:https://pan.baidu.com/s/1ckbw5pJJlKWEtK3j_XDYCw

提取码:57cl

--来自百度网盘超级会员V6的分享

下面是使用DSView软件查看输入和输出变量之间关系的步骤:

1、打开DSView软件,然后选择“打开”菜单,并选择dsl文件。

2、在DSView的主界面中,选择“波形视图”选项卡。

3、在波形视图中,点击“添加信号”按钮,然后在弹出的对话框中,选择输入和输出变量。

4、调整时间轴和垂直轴的范围,使得输入和输出变量的波形能够完整显示。

5、在波形视图中,可以查看输入和输出变量之间的关系,例如输入变量对输出变量的影响等。

还可以使用DSView的其他功能来查看输入和输出变量之间的关系,例如十进制视图、十六进制视图、二进制视图、表格视图、事件表格视图和状态表格视图等。

从图片中看,可以分析出四个输入和四个输出之间的逻辑关系。

输入A和输出Y1之间的关系为:当A为高电平时,Y1输出高电平;当A为低电平时,Y1输出低电平。

输入B和输出Y2之间的关系为:当B为高电平时,Y2输出高电平;当B为低电平时,Y2输出低电平。

输入C和输出Y3之间的关系为:当C为高电平时,Y3输出低电平;当C为低电平时,Y3输出高电平。

输入D和输出Y4之间的关系为:当D为高电平时,Y4输出低电平;当D为低电平时,Y4输出高电平。

对应的Verilog HDL代码如下:

module logic_circuit(

input A,

input B,

input C,

input D,

output Y1,

output Y2,

output Y3,

output Y4

);

assign Y1 = A;

assign Y2 = B;

assign Y3 = !C;

assign Y4 = !D;

endmodule

从波形上看,虽然没时钟,但是存在 latch 逻辑,不能用简单的组合逻辑来分析。

能提供 CPLD 这 8 个管脚信号的相关电路图,将有助于逻辑分析

逻辑电路波形图怎么画_与门逻辑电路知识点归纳

借鉴下

https://blog.csdn.net/weixin_31774171/article/details/113708816