为什么要先拉低SCL,再拉低SDA

问题 :为什么要先拉低SCL,再拉低SDA,根据读取时序图不应先拉低SDA,再拉低SCL

```c

//1.先拉低SCL,再拉低SDA

//2.拉高SCL

//3.拉低SCL## 标题

void I2C_Ack(void)

{

IIC_SCL=0; //先拉低SCL,使得SDA数据可以发生改变

IIC_SDA=0;

delay_us(2);

IIC_SCL=1;

delay_us(5);

IIC_SCL=0;

}

```

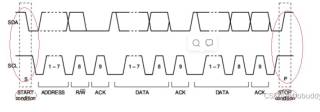

仔细看看这I2C的时序图,在scl为高时改变sda只能在开始和结束位。

其他的位只能在scl为低时改变sda,包括你代码中的ack

对于反馈有效应答位ACK的要求是:接收器在第9个时钟脉冲之前的低电平期间将数据线SDA拉低,并且确保在该时钟的高电平期间为稳定的低电平。 如果接收器是主控器,则在它收到最后一个字节后,发送一个NACK信号,以通知被控发送器结束数据发送,并释放数据线SDA,以便主控接收器发送一个停止信号P。

————————————————

版权声明:本文为CSDN博主「狂飙的笨牛」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/qq_53918631/article/details/124810934

假如先拉低sda会发生什么?

slc高电平的时候去拉低数据线,重新发一个start。