用verilog HDL语法编写4

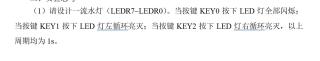

请编写程序,可以给出仿真图,题目如下图,请按题目要求编写,并给出程序。

module led_play

(

input clk, //0.5MHz 时钟

input key0, //按键,低电平按下,高电平抬起

input key1, //按键,低电平按下,高电平抬起

input key2, //按键,低电平按下,高电平抬起

output [7:0] ledr //8 个流水灯,左边高位 ledr[7] ,右边低位 ledr[0]

);

//三个按键,假定优先级 key0>key1>key2

parameter CLK_IN_FREQ = 500*1000; //0.5MHz

reg clk1s = 0; //1Hz 秒脉冲

reg clk1_ck = 0; //1Hz 方波,闪烁脉冲

reg [31:0] cnt = 0;

reg [7:0] led_cnt = 0;

reg [1:0] led_st = 0; //按键状态

assign ledr = clk1_ck == 0 ? led_cnt:~led_cnt;

always @(posedge clk)

begin

if(cnt < CLK_IN_FREQ-1)

begin

cnt <= cnt + 1;

clk1s <= 0;

end

else

begin

cnt <= 0;

clk1s <= 1;

end

end

always @(posedge clk)

begin

if(cnt == CLK_IN_FREQ/2-1 || cnt == CLK_IN_FREQ-1)

begin

clk1_ck <= ~clk1_ck;

end

end

always @(posedge clk or negedge key0)

begin

if( key0 == 0 ) //key0 按下

led_st <= 0;

else if( key1 == 0 ) //key1 按下

led_st <= 1;

else if( key2 == 0 ) //key1 按下

led_st <= 2;

end

always @(posedge clk or negedge key0)

begin

if( key0 == 0 ) //key0 按下

led_cnt <= 8'b1111_1111;

else if(key1 == 0)

led_cnt <= 8'b1111_1110;

else if(key2 == 0)

led_cnt <= 8'b0111_1111;

else if(clk1s == 1) //1Hz 秒脉冲

begin

if( led_st == 1 ) //key1 按下

led_cnt <= {led_cnt[6:0],led_cnt[7]}; //左循环

else if( led_st == 2 ) //key2 按下

led_cnt <= {led_cnt[0],led_cnt[7:1]}; //右循环

end

end

endmodule