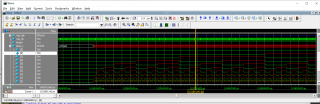

modelsim仿真出现不定值

modelsim仿真,出现下图问题,请问为什么呢?

自己检查代码好长时间,发现代码也没逻辑问题啊,并且输出控制pixel_x的信号波形,发现波形也对的上,不知道为啥这里出来个不定值x

代码问题

代码贴出来,贴在代码区里

插入代码块没有verilog语言,各位凑活着看吧[😂]

module vga_colorbar(

input sys_clk,

input sys_rst_n,

output wire vga_hs,

output wire vga_vs,

output wire[15:0]vga_rgb

);

wire vga_clk;

wire locked;

wire [9:0] pixel_x;

wire [9:0] pixel_y;

wire [15:0]pixel_data;

wire vga_en;

wire [9:0] cnt_h;

wire [9:0] cnt_v;

wire data_req;

assign rst_n = sys_rst_n && locked;

ip_core ip_core_inst (

.areset ( ~sys_rst_n ),

.inclk0 ( sys_clk ),

.c0 ( vga_clk ),

.locked ( locked )

);

vga_driver vga_driver_inst(

.vga_clk(vga_clk),

.sys_rst_n(rst_n),

.pixel_data(pixel_data),

.vga_hs(vga_hs),

.vga_vs(vga_vs),

.vga_rbg(vga_rgb),

.vga_en(vga_en),

.cnt_h(cnt_h),

.cnt_v(cnt_v),

.data_req(data_req),

.pixel_x(pixel_x),

.pixel_y(pixel_x)

);

vga_display vga_display_inst(

.vga_clk(vga_clk),

.sys_rst_n(rst_n),

.pixel_x(pixel_x),

.pixel_y(pixel_x),

.pixel_data(pixel_data)

);

endmodule

module vga_driver(

input vga_clk,

input sys_rst_n,

input [15:0] pixel_data, //像素点数据

output wire vga_hs,//行同步信号

output wire vga_vs,//场同步信号

output wire [15:0] vga_rbg,//红绿蓝三原色

output wire vga_en,

output reg [9:0] cnt_h,

output reg [9:0] cnt_v,

output wire data_req,

output wire [9:0] pixel_x,

output wire [9:0] pixel_y

);

parameter H_SYNC = 96,//行同步

H_BACK = 48,//行显示后沿

H_DISP = 640,//行有效数据

H_FRONT = 16,//行显示前沿

H_TOTAL = 800,//行扫描周期

V_SYNC = 2,//场同步

V_BACK = 33,//场显示后沿

V_DISP = 480,//场有效数据

V_FRONT = 10,//场显示前沿

V_TOTAL = 525;//场扫描周期

//场计数

always@(posedge vga_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

cnt_h <= 0;

else if(cnt_h==H_TOTAL-1)

cnt_h <= 0;

else

cnt_h <= cnt_h+1;

end

//行计数

always@(posedge vga_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

cnt_v <= 0;

else if(cnt_h==H_TOTAL-1)begin

if(cnt_v==V_TOTAL-1)

cnt_v <= 0;

else

cnt_v <= cnt_v+1;

end

else

cnt_v <= cnt_v;

end

assign vga_hs = cnt_h<H_SYNC ? 1'b0:1'b1;

assign vga_vs = cnt_v<V_SYNC ? 1'b0:1'b1;

assign vga_en = ((cnt_h>=H_SYNC+H_BACK&&cnt_h<H_SYNC+H_BACK+H_DISP) &&

(cnt_v>=V_SYNC+V_BACK&&cnt_v<V_SYNC+V_BACK+V_DISP)) ? 1'b1:1'b0;

assign vga_rgb = vga_en ? pixel_data:16'd0;

//请求像素点颜色数据输入,提前一个时钟周期

assign data_req = ((cnt_h>=H_SYNC+H_BACK-1&&cnt_h<H_SYNC+H_BACK+H_DISP-1) &&

(cnt_v>=V_SYNC+V_BACK&&cnt_v<V_SYNC+V_BACK+V_DISP)) ? 1'b1:1'b0;

assign pixel_x = data_req ? (cnt_h-(H_SYNC+H_BACK-1)) : 10'd0;

assign pixel_y = data_req ? (cnt_v-(V_SYNC+V_BACK-1)) : 10'd0;

endmodule

module vga_display(

input vga_clk,

input sys_rst_n,

input [9:0] pixel_x,

input [9:0] pixel_y,

output reg [15:0]pixel_data

);

parameter H_DISP = 640;

parameter V_DISP = 480;

localparam WHITE = 16'b11111_111111_11111;

localparam BLACK = 16'b00000_000000_00000;

localparam RED = 16'b11111_000000_00000;

localparam GREEN = 16'b00000_111111_00000;

localparam BLUE = 16'b00000_000000_11111;

always@(posedge vga_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

pixel_data <= 16'd0;

else if((pixel_x>=0) && (pixel_x<H_DISP/5))

pixel_data <= WHITE;

else if((pixel_x>=H_DISP/5) && (pixel_x<(H_DISP/5)*2))

pixel_data <= BLACK;

else if((pixel_x>=(H_DISP/5)*2) && (pixel_x<(H_DISP/5)*3))

pixel_data <= RED;

else if((pixel_x>=(H_DISP/5)*3) && (pixel_x<(H_DISP/5)*4))

pixel_data <= GREEN;

else

pixel_data <= BLUE;

end

endmodule

`timescale 1ns/1ps

module tb_vga_colorbar();

reg sys_clk,sys_rst_n;

wire vga_hs,vga_vs;

wire [15:0] vga_rgb;

initial begin

sys_clk <= 1;

sys_rst_n <= 0;

#20 sys_rst_n <= 1;

end

always #10 sys_clk <= ~sys_clk;

vga_colorbar vga_colorbar_inst(

.sys_clk(sys_clk),

.sys_rst_n(sys_rst_n),

.vga_hs(vga_hs),

.vga_vs(vga_vs),

.vga_rgb(vga_rgb)

);

endmodule