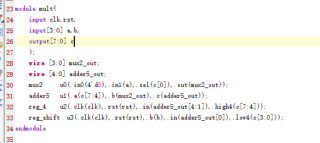

verilog如何让仿真进行一定次数就停止

我写了一位原码乘法器,希望他进行四次运算就结束本次运算,请问如何实现?还有一个问题什么也不写,是默认一直循环进行这个运算吗?感谢!

`timescale 1ns/1ns

module testbench;

reg rst;

reg clk;

reg [3:0] a;

reg [3:0] b;

wire[7:0] c;

parameter RESET_PERIOD = 500;

parameter CLK_PERIOD = 100; //10MHz

initial clk = 0;

always clk = #(CLK_PERIOD/2.0) ~clk;

initial begin

rst = 1;

#RESET_PERIOD

rst = 0;

#(CLK_PERIOD*4) $stop; // 执行 4 个时钟之后停止

end

//////////////////////////////////////////////////////////////////////

// 这部分代码是自动产生2个4位数 a,b 每个时钟变化一次

always@(posedge clk)

begin

if(rst)

begin

a <= #1 0;

b <= #1 1;

end

else

begin

{b,a} <= #1 {b,a} + 1;

end

end

//////////////////////////////////////////////////////////////////////

// 要是不用上自动产生2个4位数,可以按下面的代码

//initial begin

// a = 0;b = 0;

// #RESET_PERIOD

// a = 1;b = 2;

// #CLK_PERIOD

// a = 3;b = 4;

// #CLK_PERIOD

// a = 5;b = 6;

//end

//////////////////////////////////////////////////////////////////////

mult ux

(

.clk (clk),

.rst (rst),

.a (a),

.b (b),

.c (c)

);

endmodule