FPGA的120+普通IO,逻辑为0时(电压为0V),希望输出电平为1.2V,逻辑为1时(电压为1.2V),希望输出电平为2.4V,要怎么设计

FPGA的120+个普通IO,逻辑为0时(电压为0V),希望输出电平为1.2V,逻辑为1时(电压为1.2V),希望输出电平为2.4V,要怎么设计

以 XILINX FPGA举例

FPGA 管脚若干个 BANK 组成

每个BANK内的管脚的电压必须是一样的。

不同BANK的管脚的电压可以不一样。

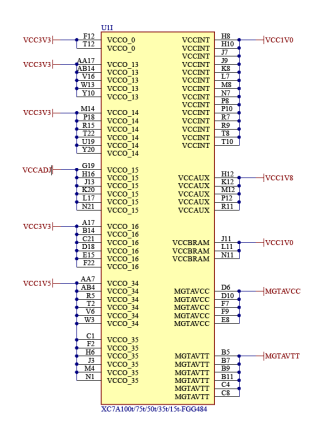

比如 XC7A100T 芯片的管脚供电图如下。

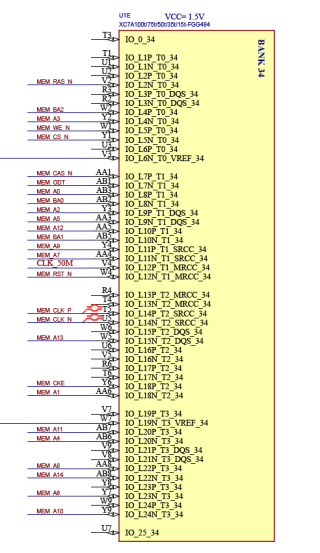

BANK34 的管脚是 1.5V

你可以将 1.2V 的管脚放在 BANK16上,2.5V 的管脚放在 BANK15上

按下图照葫芦画瓢, VCCO_15 接2.5V,VCCO_16接1.2V