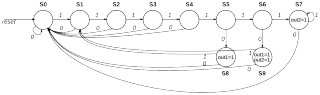

有限状态机问题,组合逻辑部分

第一种写法为什么会出问题

module top_module(

input in,

input [9:0] state,

output [9:0] next_state,

output out1,

output out2);

parameter S0 = 10'b0000000001,

S1 = 10'b0000000010,

S2 = 10'b0000000100,

S3 = 10'b0000001000,

S4 = 10'b0000010000,

S5 = 10'b0000100000,

S6 = 10'b0001000000,

S7 = 10'b0010000000,

S8 = 10'b0100000000,

S9 = 10'b1000000000;

always @(*) begin

case(state)

S0: next_state = in?S1:S0;

S1: next_state = in?S2:S0;

S2: next_state = in?S3:S0;

S3: next_state = in?S4:S0;

S4: next_state = in?S5:S0;

S5: next_state = in?S6:S8;

S6: next_state = in?S7:S9;

S7: next_state = in?S7:S0;

S8: next_state = in?S1:S0;

S9: next_state = in?S1:S0;

endcase

end

assign out1 = (state == S8) || (state == S9);

assign out2 = (state == S7) || (state == S9);

endmodule

module top_module(

input in,

input [9:0] state,

output [9:0] next_state,

output out1,

output out2);

parameter S0 = 4'd0;

parameter S1 = 4'd1;

parameter S2 = 4'd2;

parameter S3 = 4'd3;

parameter S4 = 4'd4;

parameter S5 = 4'd5;

parameter S6 = 4'd6;

parameter S7 = 4'd7;

parameter S8 = 4'd8;

parameter S9 = 4'd9;

assign next_state[0] = ~in & (state[S0] | state[S1] | state[S2] | state[S3] | state[S4] | state[S7] | state[S8] | state[S9]);

assign next_state[1] = in & (state[S0] | state[S8] | state[S9]);

assign next_state[2] = in & state[S1];

assign next_state[3] = in & state[S2];

assign next_state[4] = in & state[S3];

assign next_state[5] = in & state[S4];

assign next_state[6] = in & state[S5];

assign next_state[7] = in & (state[S6] | state[S7]);

assign next_state[8] = ~in & state[S5];

assign next_state[9] = ~in & state[S6];

assign out1 = (state[S8] | state[S9]);

assign out2 = (state[S7] | state[S9]);

endmodule

手机上看的费劲,没仔细分析第一种的逻辑。但是有个错误需要你更正。

组合逻辑下 case 条件要写全,你的代码中没有写全。需要加个 default 。

module top_module(

input in,

input [9:0] state,

output [9:0] next_state,

output out1,

output out2);

reg [3:0] i;

parameter S0 = 10'b0000000001,

S1 = 10'b0000000010,

S2 = 10'b0000000100,

S3 = 10'b0000001000,

S4 = 10'b0000010000,

S5 = 10'b0000100000,

S6 = 10'b0001000000,

S7 = 10'b0010000000,

S8 = 10'b0100000000,

S9 = 10'b1000000000,

S10 = 10'b0000000000;

always @(*) begin

next_state=S10;

for(i=0;i<10;i=i+1)begin

case(state&(1<<i))

S0: next_state = next_state|(in?S1:S0);

S1: next_state = next_state|(in?S2:S0);

S2: next_state = next_state|(in?S3:S0);

S3: next_state = next_state|(in?S4:S0);

S4: next_state = next_state|(in?S5:S0);

S5: next_state = next_state|(in?S6:S8);

S6: next_state = next_state|(in?S7:S9);

S7: next_state = next_state|(in?S7:S0);

S8: next_state = next_state|(in?S1:S0);

S9: next_state = next_state|(in?S1:S0);

default:next_state = next_state|S10;

endcase

end

end

assign out1 = (state & S8) == S8 || (state & S9) == S9;

assign out2 = (state & S7) == S7 || (state & S9) == S9;

//assign out1 = (state == S8) || (state == S9);

//assign out2 = (state == S7) || (state == S9);

endmodule