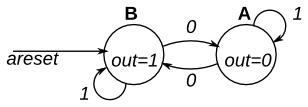

HDLbits有限状态机写法

HDLbits里的状态机写法,下面这两种写法有什么不一样吗,为什么第一种就仿真结果错误

module top_module(

input clk,

input areset, // Asynchronous reset to state B

input in,

output out);//

parameter A=0, B=1;

reg state, next_state;

always @(*) begin // This is a combinational always block

// State transition logic

case(state)

A:begin

if(in)begin

next_state = A;

out = 1'b0;

end

else begin

next_state = B;

out = 1'b1;

end

end

B:begin

if(in) begin

next_state = B;

out = 1'b1;

end

else begin

next_state = A;

out = 1'b0;

end

end

endcase

end

always @(posedge clk, posedge areset) begin // This is a sequential always block

// State flip-flops with asynchronous reset

if(areset)

state <= B;

else

state <= next_state;

end

// Output logic

//assign out = (state == B);// assign out = (state == ...);

endmodule

module top_module(

input clk,

input areset, // Asynchronous reset to state B

input in,

output out);//

parameter A=0, B=1;

reg state, next_state;

always @(*) begin // This is a combinational always block

case(state)

A:begin

if(in == 1'b1)begin

next_state <= A;

end

else begin

next_state <= B;

end

end

B:begin

if(in == 1'b1)begin

next_state <= B;

end

else begin

next_state <= A;

end

end

endcase

end

always @(posedge clk, posedge areset) begin // This is a sequential always block

if(areset)begin

state <= B;

end

else begin

state <= next_state;

end

end

// Output logic

assign out = (state == B);

endmodule

第一种代码中

out 的值与 in 有逻辑关联,这是不对的

可以按如下更改,综合后的结果应该和第二种代码一样

module top_module(

input clk,

input areset, // Asynchronous reset to state B

input in,

output out);//

parameter A=0, B=1;

reg state, next_state;

always @(*) begin // This is a combinational always block

// State transition logic

case(state)

A:begin

out = 1'b0;

if(in)begin

next_state = A;

end

else begin

next_state = B;

end

end

B:begin

out = 1'b1;

if(in) begin

next_state = B;

end

else begin

next_state = A;

end

end

endcase

end

always @(posedge clk, posedge areset) begin // This is a sequential always block

// State flip-flops with asynchronous reset

if(areset)

state <= B;

else

state <= next_state;

end

// Output logic

//assign out = (state == B);// assign out = (state == ...);

endmodule