用quartus prime设计可控的100进制可逆计数器

要求用fpga开发板下载

计数器的时钟输入信号周期为1s

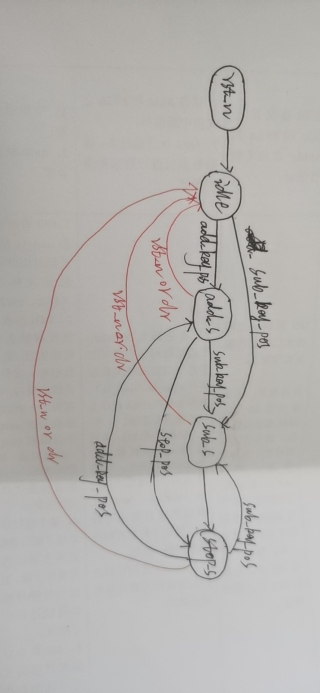

有一个复位clr和两个控制端plus和minus

使计数器有复位 增或减计数 暂停功能

保证有偿

1、按键需要通过边沿检测处理:

always @ (posedge clk )

begin

key_buf0 <= plus_key;

key_buf1 <= key_buf0;

end

assign plus_pos = !key_buf1 && key_buf0;

assign plus_neg = key_buf1 && (!key_buf0);

2、

无论那种开发板,就是先确定按键接线方式,如何扫描每一个键的状态,这些按键按下之后,进行何种操作

主函数主要是启动中断服务,一个是计数中断,一个是按键扫描中断,可逆服务由按键扫描中断提供

仅供参考

module cnt100

(

clk ,

clr ,

plus ,

minus ,

high_b , //10位数

low_b //个位数

);

input clk ;

input clr ;

input plus ;

input minus ;

output [3:0] high_b ;//10位数

output [3:0] low_b ;//个位数

reg [3:0] high_b ;//10位数

reg [3:0] low_b ;//个位数

always (posedge clk)

begin

if (clr)

low_b <= 4'b0 ;//同步清零

else if (plus) //加

begin

if (low_b == 4'b1001)

low_b <= 4'b0 ;

else

low_b <= low_b + 1;

end

else if (minus)//减

begin

if (low_b == 4'b0 )

low_b <= 4'b1001 ;

else

low_b <= low_b - 1;

end

else //暂停

low_b <= low_b ;

end

always (posedge clk)

begin

if (clr)

high_b <= 4'b0 ;//同步清零

else if (plus && (low_b == 4'b1001 )) //进位

begin

if (high_b == 4'b1001)

high_b <= 4'b0 ;

else

high_b <= high_b + 1;

end

else if (minus && (low_b == 4'b0000 ))//借位

begin

if (high_b == 4'b0 )

high_b <= 4'b1001 ;

else

high_b <= high_b - 1;

end

else //暂停

high_b <= high_b ;

end

endmodule