quartusII 12.1 调用modelsim 10.1b仿真无信号输出

VHDL程序为

library IEEE;

use IEEE.Std_logic_1164.all;

entity test_HCT688 is

port(Q, P : in std_logic_vector(7 downto 0);

GBAR : in std_logic; PEQ : out std_logic);

end test_HCT688;

architecture VER1 of test_HCT688 is

begin

PEQ <= '0' when ((To_X01(P) = To_X01(Q)) and (GBAR = '0')) else '1';

end VER1;

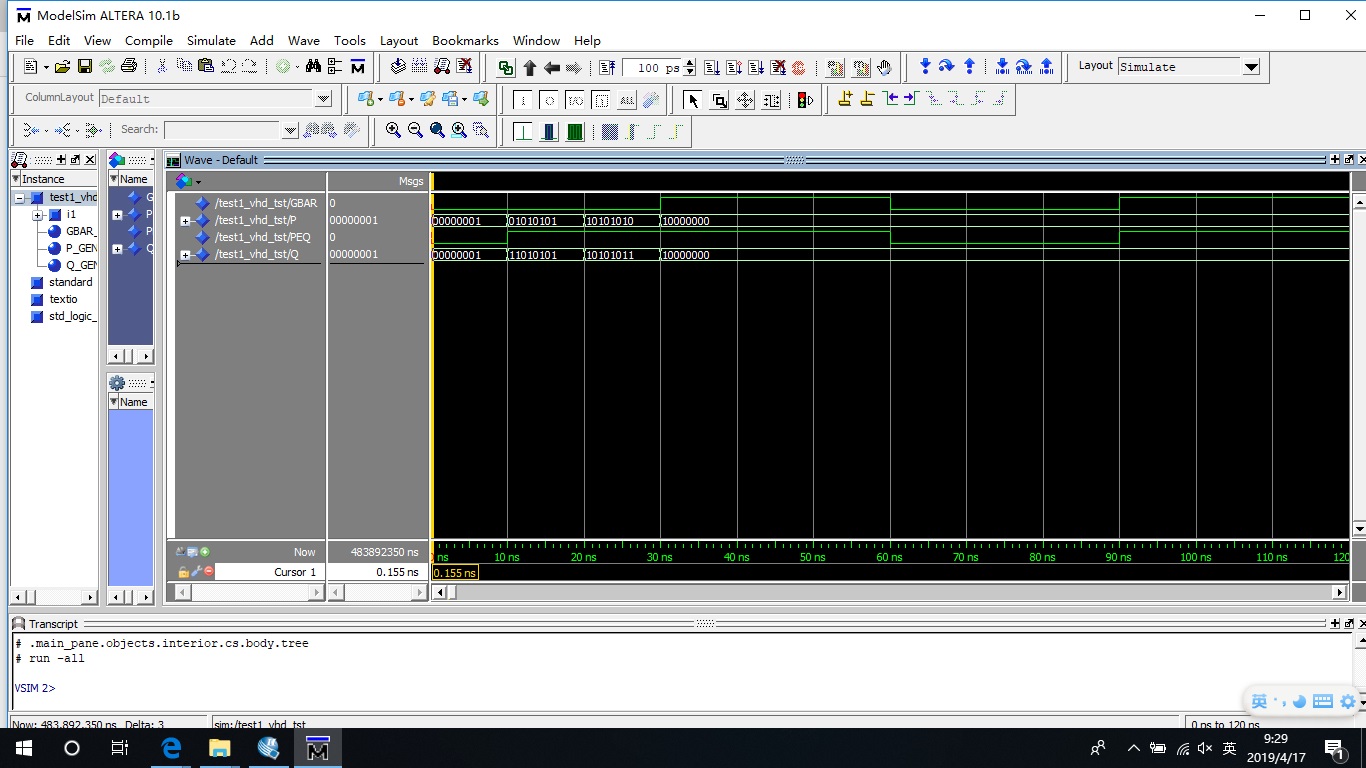

使用modelsim仿真无输出波形,testbench文件为:

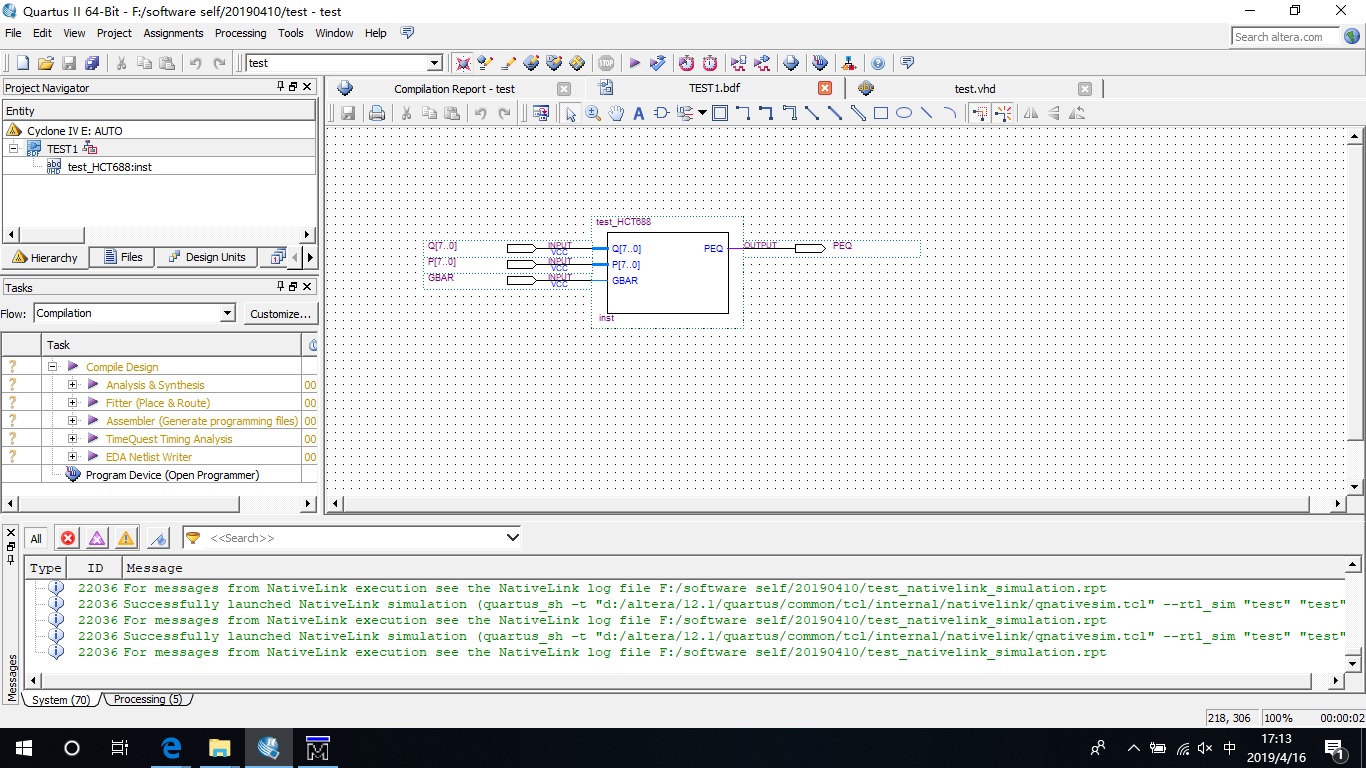

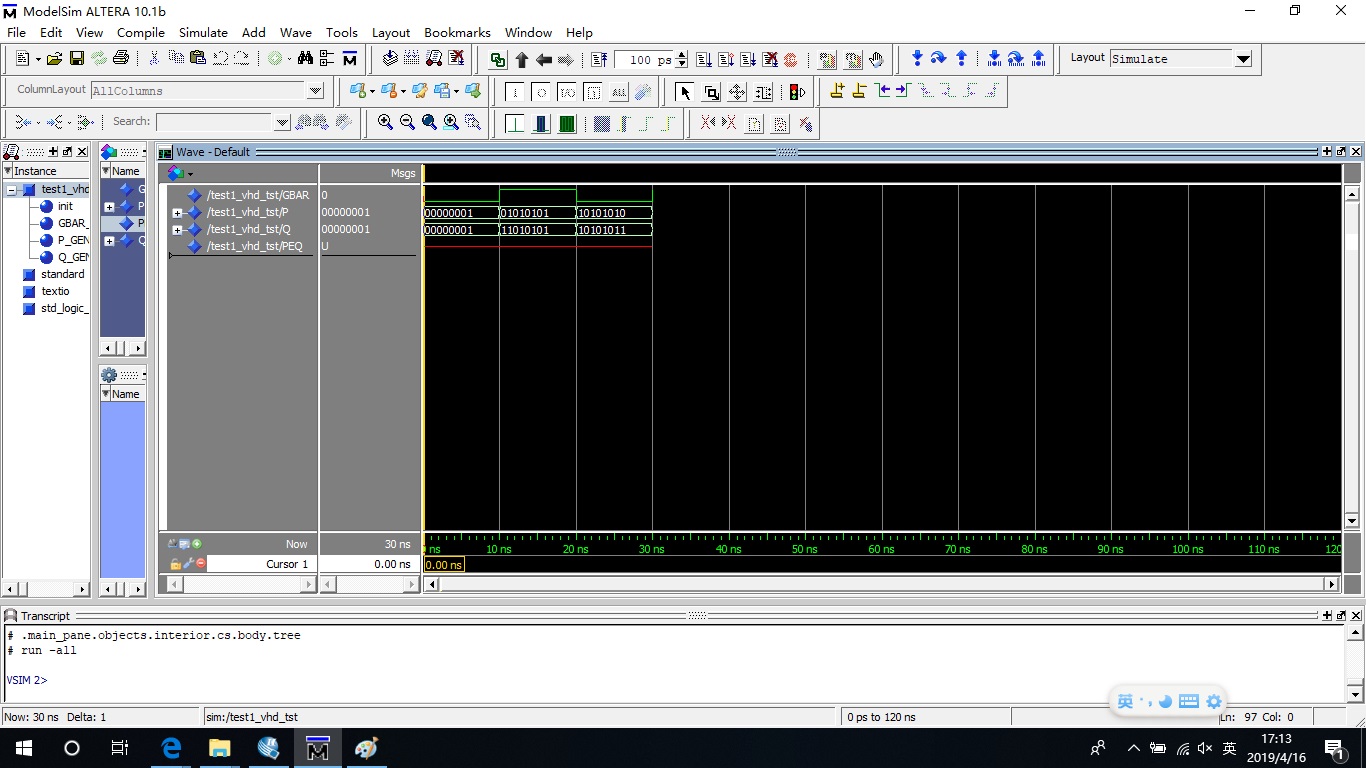

后来用代码写顶层文件,然后用testbench仿真,就ok。但是画原理图,用testbench仿真,就出错: ** Warning: (vsim-3473) Component instance "i1 : TEST1" is not bound. 最后用原理图生成.vhd文件,然后再进行仿真。顶层代码为:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY work;

ENTITY TEST1 IS

PORT

(

GBAR : IN STD_LOGIC;

P : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

Q : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

PEQ : OUT STD_LOGIC

);

END TEST1;

ARCHITECTURE bdf_type OF TEST1 IS

COMPONENT test_hct688

PORT(GBAR : IN STD_LOGIC;

P : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

Q : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

PEQ : OUT STD_LOGIC

);

END COMPONENT;

BEGIN

b2v_inst : test_hct688

PORT MAP(GBAR => GBAR,

P => P,

Q => Q,

PEQ => PEQ);

END bdf_type;

最后,有没有大神知道个中缘由?