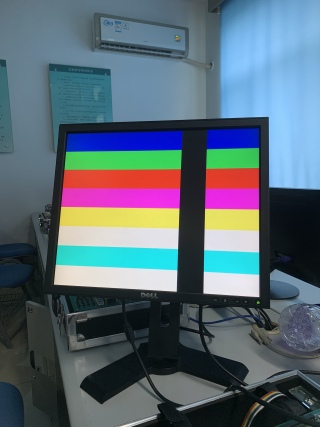

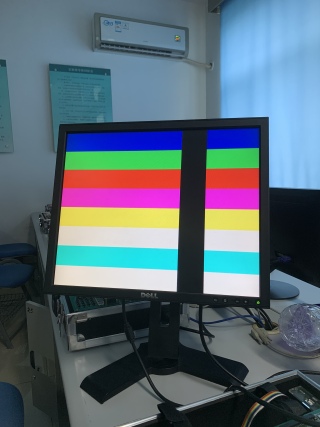

fpga的vga色彩条显示问题

//VGA彩条信号发生器源代码

/*引脚定义

Clock50MHz 输入时钟采用50MHz

key 彩条选择信号为"00"时显示竖彩条为"01"时显示横彩条其他情况显示棋

盘格

rgb 输出三基色

hs 行同步信号

vs 场同步信号 */

module color(clock50MHz,key,rgb,hs,vs);

input clock50MHz; input[1:0] key; output hs,vs; output[2:0] rgb;

reg hs,vs,clock; reg[2:0] rgb,rgbx,rgby; reg[9:0] hcnt,vcnt;

parameter h_Ta=96,h_Tb=40,h_Tc=8,h_Td=640,h_Te=8,h_Tf=8,h_Tg=800;

parameter v_Ta=2,v_Tb=25,v_Tc=8,v_Td=480,v_Te=8,v_Tf=2,v_Tg=525;

always@(posedge clock50MHz) //2分频得到25MHz的频率

begin clock<=~clock; end

always@(posedge clock) //行计数800

begin if(hcnt==h_Tg-1) hcnt<=0; else hcnt<=hcnt+1;end

always@(negedge hs) //场计数525

begin if(vcnt==v_Tg-1) vcnt<=0; else vcnt<=vcnt+1;end

always@(posedge clock) //时钟clock为25MHz

begin if(hcnt<=h_Ta-1) hs<=0; //产生行同步信号

else hs<=1; end

always@(vcnt)

begin if(vcnt<=v_Ta-1) vs<=0; //产生场同步信号

else vs<=1; end

always@(posedge clock)

begin //竖彩条 说明显示的位置及颜色

if(hcnt<=h_Ta+h_Tb+h_Tc-1) rgbx<=3'b000; //黑色

else if(hcnt<=h_Ta+h_Tb+h_Tc+80-1) rgbx<=3'b001; //红

else if(hcnt<=h_Ta+h_Tb+h_Tc+160-1) rgbx<=3'b010; //绿

else if(hcnt<=h_Ta+h_Tb+h_Tc+240-1) rgbx<=3'b100; //蓝

else if(hcnt<=h_Ta+h_Tb+h_Tc+320-1) rgbx<=3'b101; //青

else if(hcnt<=h_Ta+h_Tb+h_Tc+400-1) rgbx<=3'b110; //品

else if(hcnt<=h_Ta+h_Tb+h_Tc+480-1) rgbx<=3'b000; //黑

else if(hcnt<=h_Ta+h_Tb+h_Tc+560-1) rgbx<=3'b011; //黄

else if(hcnt<=h_Ta+h_Tb+h_Tc+640-1) rgbx<=3'b111; //白

else rgbx<=3'b000;

if(vcnt<=v_Ta+v_Tb+v_Tc-1) rgby<=3'b000; /*横彩条说明显示的位置及颜

色*/

else if(vcnt<=v_Ta+v_Tb+v_Tc+60-1) rgby<=3'b001;

else if(vcnt<=v_Ta+v_Tb+v_Tc+120-1) rgby<=3'b010;

else if(vcnt<=v_Ta+v_Tb+v_Tc+180-1) rgby<=3'b100;

else if(vcnt<=v_Ta+v_Tb+v_Tc+240-1) rgby<=3'b101;

else if(vcnt<=v_Ta+v_Tb+v_Tc+300-1) rgby<=3'b110;

else if(vcnt<=v_Ta+v_Tb+v_Tc+360-1) rgby<=3'b111;

else if(vcnt<=v_Ta+v_Tb+v_Tc+420-1) rgby<=3'b011;

else if(vcnt<=v_Ta+v_Tb+v_Tc+480-1) rgby<=3'b111;

else rgby<=3'b000;

end

always @(key)

begin if(key==2'b00) rgb<=rgbx;

else if(key==2'b01) rgb<=rgby;

else if(key==2'b10) rgb<=(rgbx+rgby);

else rgb<=(rgbx-rgby);

end

endmodule

这个代码应该没问题了。红包就不用了。没问题就点"采纳"吧

//VGA彩条信号发生器源代码

/*引脚定义

Clock50MHz 输入时钟采用50MHz

key 彩条选择信号为"00"时显示竖彩条为"01"时显示横彩条其他情况显示棋

盘格

rgb 输出三基色

hs 行同步信号

vs 场同步信号 */

module color(clock50MHz,key,rgb,hs,vs);

input clock50MHz; input[1:0] key; output hs,vs; output[2:0] rgb;

reg hs,vs,clock; reg[2:0] rgb,rgby; reg[9:0] hcnt,vcnt;

reg[3:0] rgbx;

parameter h_Ta=96,h_Tb=40,h_Tc=8,h_Td=640,h_Te=8,h_Tf=8,h_Tg=800;

parameter v_Ta=2,v_Tb=25,v_Tc=8,v_Td=480,v_Te=8,v_Tf=2,v_Tg=525;

always@(posedge clock50MHz) //2分频得到25MHz的频率

begin clock<=~clock; end

always@(posedge clock) //行计数800

begin if(hcnt==h_Tg-1) hcnt<=0; else hcnt<=hcnt+1;end

always@(negedge hs) //场计数525

begin if(vcnt==v_Tg-1) vcnt<=0; else vcnt<=vcnt+1;end

always@(posedge clock) //时钟clock为25MHz

begin if(hcnt<=h_Ta-1) hs<=0; //产生行同步信号

else hs<=1; end

always@(vcnt)

begin if(vcnt<=v_Ta-1) vs<=0; //产生场同步信号

else vs<=1; end

always@(posedge clock)

begin //竖彩条 说明显示的位置及颜色

if(hcnt<=h_Ta+h_Tb+h_Tc-1) rgbx<=4'b0000; //黑色

else if(hcnt<=h_Ta+h_Tb+h_Tc+80-1) rgbx<=4'b1001; //红

else if(hcnt<=h_Ta+h_Tb+h_Tc+160-1) rgbx<=4'b1010; //绿

else if(hcnt<=h_Ta+h_Tb+h_Tc+240-1) rgbx<=4'b1100; //蓝

else if(hcnt<=h_Ta+h_Tb+h_Tc+320-1) rgbx<=4'b1101; //青

else if(hcnt<=h_Ta+h_Tb+h_Tc+400-1) rgbx<=4'b1110; //品

else if(hcnt<=h_Ta+h_Tb+h_Tc+480-1) rgbx<=4'b1000; //黑

else if(hcnt<=h_Ta+h_Tb+h_Tc+560-1) rgbx<=4'b1011; //黄

else if(hcnt<=h_Ta+h_Tb+h_Tc+640-1) rgbx<=4'b1111; //白

else rgbx<=4'b0000;

if(vcnt<=v_Ta+v_Tb+v_Tc-1) rgby<=3'b000; /*横彩条说明显示的位置及颜色*/

else if(vcnt<=v_Ta+v_Tb+v_Tc+60-1) rgby<=3'b001;

else if(vcnt<=v_Ta+v_Tb+v_Tc+120-1) rgby<=3'b010;

else if(vcnt<=v_Ta+v_Tb+v_Tc+180-1) rgby<=3'b100;

else if(vcnt<=v_Ta+v_Tb+v_Tc+240-1) rgby<=3'b101;

else if(vcnt<=v_Ta+v_Tb+v_Tc+300-1) rgby<=3'b110;

else if(vcnt<=v_Ta+v_Tb+v_Tc+360-1) rgby<=3'b111;

else if(vcnt<=v_Ta+v_Tb+v_Tc+420-1) rgby<=3'b011;

else if(vcnt<=v_Ta+v_Tb+v_Tc+480-1) rgby<=3'b111;

else rgby<=3'b000;

end

always @(key)

begin

if(key==2'b00) rgb<=rgbx[2:0];

else if(key==2'b01) rgb<=rgbx[3] == 0 ? 3'b000:rgby;

else if(key==2'b10) rgb<=rgbx[3] == 0 ? 3'b000:(rgbx[2:0]+rgby);

else rgb<=rgbx[3] == 0 ? 3'b000:(rgbx[2:0]-rgby);

end

endmodule

代码没法看,你把代码贴在代码区。

代码看不出来问题。不排除硬件等其他问题。

可以试着修改第 53行,改为

else if(key==2'b01) rgb<=rgbx==3'b000 ? 3'b000:rgby;

如果不行,就需要仿真看波形。