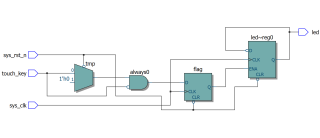

verilog边沿检测实现触摸控制小灯翻转

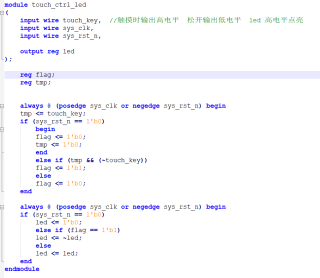

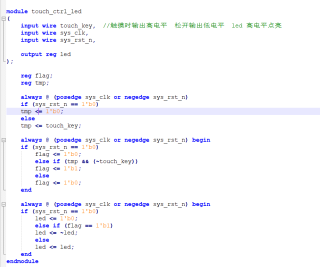

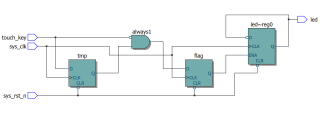

1和2为一组图 3和4为一组图

为什么tmp的赋值要单独用一个always块 才能实现延一拍的效果

在3/4 中tmp的赋值单独用一个always块 ,这么做比较好理解,逻辑也比较清晰。

你在 1/2 中 可以这么改

module touch_ctrl led

(

input wire touch_key, //松开输出低电平 触摸时输出高电平 1ed高电平点亮

input wire sys_clk,

input wire sys_rst_n,

output reg led

);

reg flag;

reg tmp = 0; //在FPGA 中这么定义赋初始值是允许的,在一些 芯片设计中是不能这么做的。

always @(posedge sys_clk or negedge sys_rst_n) begin

tmp<= touch key;

if(sys_rst_n== 1'b0)

begin

flag <=1'b0;

// tmp <=1'b0; //这个地方会覆盖上面 tmp 的值,逻辑会比较乱,将这行去掉。

end

else if(tmp && (~touch_key))

flag 1'b1;

else

flag<=1'b0;

end

always @(posedge sys_clk or negedge sys_rst_n) begin

if(sys_rst_n = 1'b0)

1ed <= 1'b0;

else if(flag==1'b1)

led <= ~led;

else

led <= led;

end

endmodule

也可以这么改

module touch_ctrl led

(

input wire touch_key, //松开输出低电平 触摸时输出高电平 1ed高电平点亮

input wire sys_clk,

input wire sys_rst_n,

output reg led

);

reg flag;

reg tmp;

always @(posedge sys_clk or negedge sys_rst_n) begin

// tmp<= touch key;

tmp <= sys_rst_n == 0 ? 0:touch_key;

if(sys_rst_n== 1'b0)

begin

flag <=1'b0;

// tmp <=1'b0; //这个地方会覆盖上面 tmp 的值,逻辑会比较乱,将这行去掉。

end

else if(tmp && (~touch_key))

flag 1'b1;

else

flag<=1'b0;

end

always @(posedge sys_clk or negedge sys_rst_n) begin

if(sys_rst_n = 1'b0)

1ed <= 1'b0;

else if(flag==1'b1)

led <= ~led;

else

led <= led;

end

endmodule