有关状态机的Verilog代码

我的状态机代码和test代码分别如下:

module transformation (a,b,s,clk,S,C,X);

input a,b,s,clk;

output S,C,X;

reg S,C,X;

always @ (posedge clk)

case(s)

0:if(a==1&b==1)begin S<=1; C<=0; end

else if(a==0&b==0)begin S<=5; C<=1; end

else begin S<=s; X<=1; end

1:if(a==1&b==0)begin S<=4; C<=1; end

else if(a==0&b==1)begin S<=3; C<=0; end

else begin S<=s; X<=1; end

2:if(a==0&b==0) begin S<=1; C<=1; end

else if(a==1&b==0)begin S<=5; C<=0; end

else begin S<=s; X<=1; end

3:if(a==0&b==0) begin S<=2; C<=0; end

else if(a==1&b==0) begin S<=4; C<=1; end

else begin S<=s; X<=1; end

4:if(a==1&b==0) begin S<=3; C<=0; end

else if(a==0&b==1) begin S<=5; C<=1; end

else begin S<=s; X<=1; end

5:if(a==0&b==0)begin S<=5; C<=0; end

else if(a==1&b==0)begin S<=0; C<=1; end

else begin S<=s; X<=1; end

endcase

endmodule

和

module test();

reg a,b,C,X,clk;

reg [0:2] s,S;

initial

begin

clk=0;

a=0;

b=0;

s=0;

S=6;

X=0;

end

always #10 a=~a;

always #5 b=~b;

always #5 clk=~clk;

always @ (posedge clk)

begin

X<=0;

if(S==6) ;

else begin s<=S; end

transformationT1(

.a(a),

.b(b),

.s(s),

.clk(clk),

.S(S),

.C(C),

.X(X)

);

end

endmodule

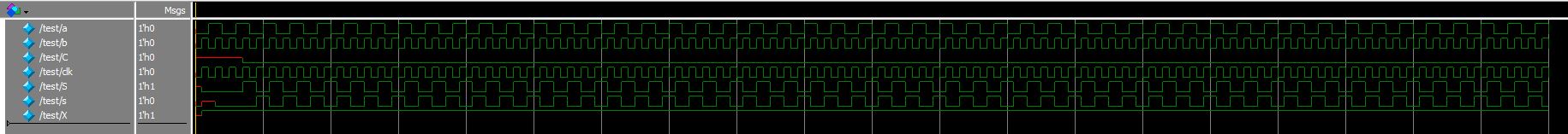

仿真后发现全部都是高阻,这是为什么啊?要怎么改呢?

两个问题,第一个问题transformation 模块好像描述的是组合电路。第二个问题,假设transformation 的功能没有问题,test程序中将transformation 放在always语句中以clk上边沿触发为条件调用,但transformation 本身也有检测时钟边沿的情况。所以transformation 接收到的信号是个高电平信号,也就是说transformation 永远也不会被触发。

状态的数字可能需要标注进制,s作为寄存器不需要在测试文件中声明,case中应有default分支用于初始化。

不对啊,你的代码在我这里根本没法编译运行。

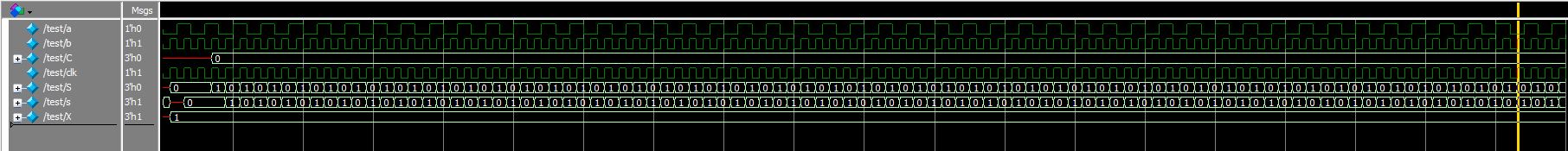

testbench改了不少东西让你的代码跑起来了,不过问题是,你如果要输出数字5,为什么只给了1位的reg定义呢?:

module test();

reg a,b,clk;

reg s;

wire S,C,X;

initial

begin

clk=0;

a=0;

b=0;

s=0;

end

always #10 a=~a;

always #5 b=~b;

always #5 clk=~clk;

always @ (posedge clk)

begin

if(S==6) ;

else begin s<=S; end

end

transformation T1(

.a(a),

.b(b),

.s(s),

.clk(clk),

.S(S),

.C(C),

.X(X)

);

endmodule

于是乎把你的源代码也改了一下,这个是不是你要的结果?看起来好像也没啥区别。。。

module test();

reg a,b,clk;

reg [2:0] s;

wire [2:0] S,C,X;

initial

begin

clk=0;

a=0;

b=0;

s=0;

end

always #10 a=~a;

always #5 b=~b;

always #5 clk=~clk;

always @ (posedge clk)

begin

if(S==6) ;

else begin s<=S; end

end

transformation T1(

.a(a),

.b(b),

.s(s),

.clk(clk),

.S(S),

.C(C),

.X(X)

);

endmodule

module test();

reg a,b,clk;

reg s;

wire S,C,X;

initial

begin

clk=0;

a=0;

b=0;

s=0;

end

always #10 a=~a;

always #5 b=~b;

always #5 clk=~clk;

always @ (posedge clk)

begin

if(S==6) ;

else begin s<=S; end

end

transformation T1(

.a(a),

.b(b),

.s(s),

.clk(clk),

.S(S),

.C(C),

.X(X)

);

endmodule