FPGA的伪随机序列发生器

求问, 用verilog编写了一个伪随机序列发生器,产生01二进制码流,仿真与signaltap信号抓取没有问题,但是连接到示波器显示的波形却像噪音一样

https://wenku.baidu.com/view/e80884a4284ac850ad0242d1.html

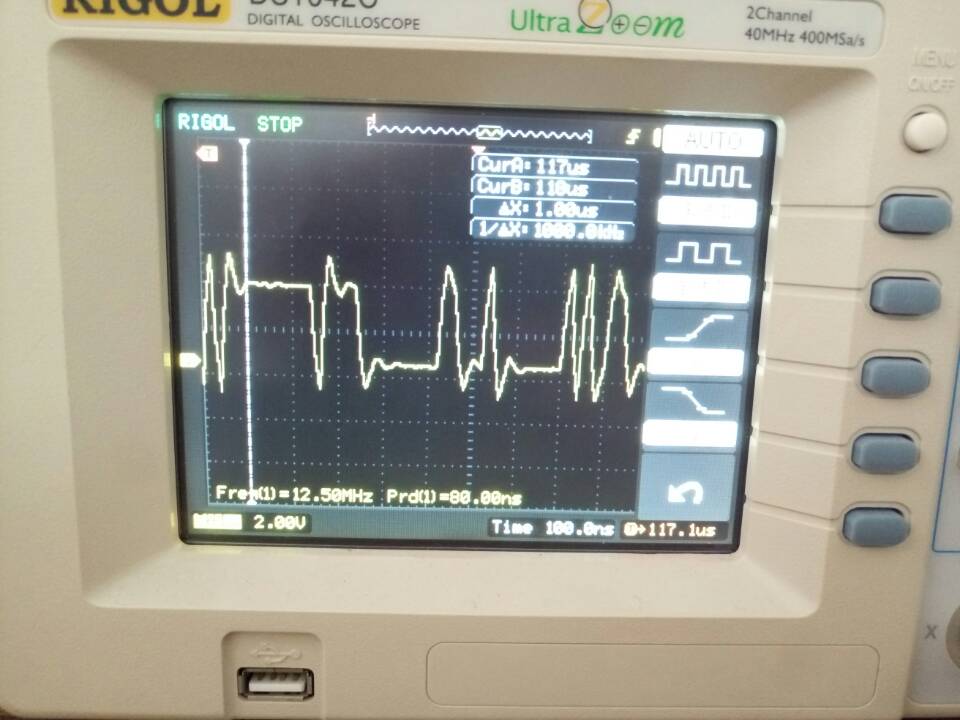

您好啊,您看看情况,这是波形图,modelsim 仿真 和 signaltap 抓取信号均没有问题,但是示波器显示波形如下图图片说明](https://img-ask.csdn.net/upload/201706/02/1496362967_971317.jpg)

这是放大后

检查一下时钟和参考地信号呢。

是用隔直电容输出的吗,电容的大小是否匹配,查看电路吧

用verilog编写了一个伪随机序列发生器,产生01二进制码流,仿真与signaltap信号抓取没有问题,但是连接到示波器显示的波形却像噪音一样,这是因为伪随机序列是周期不固定的序列 是噪声信号,需要时钟对他进行同步,,,用双通道示波器显示,同步时钟做触发,就能看到波形