QUARTUS PRIME与MODELSIM联合仿真ALTERA FFT IPCOER 问题

使用quartus与modelsim联合仿真时,fft没有输出

下面是用quartus生成的testbench然后改的

-- Copyright (C) 2016 Intel Corporation. All rights reserved.

-- Your use of Intel Corporation's design tools, logic functions

-- and other software and tools, and its AMPP partner logic

-- functions, and any output files from any of the foregoing

-- (including device programming or simulation files), and any

-- associated documentation or information are expressly subject

-- to the terms and conditions of the Intel Program License

-- Subscription Agreement, the Intel Quartus Prime License Agreement,

-- the Intel MegaCore Function License Agreement, or other

-- applicable license agreement, including, without limitation,

-- that your use is for the sole purpose of programming logic

-- devices manufactured by Intel and sold by Intel or its

-- authorized distributors. Please refer to the applicable

-- agreement for further details.

-- ***************************************************************************

-- This file contains a Vhdl test bench template that is freely editable to

-- suit user's needs .Comments are provided in each section to help the user

-- fill out necessary details.

-- ***************************************************************************

-- Generated on "04/14/2017 19:32:52"

-- Vhdl Test Bench template for design : fft

--

-- Simulation tool : ModelSim (VHDL)

--

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY fft_vhd_tst IS

END fft_vhd_tst;

ARCHITECTURE fft_arch OF fft_vhd_tst IS

-- constants

-- signals

SIGNAL clk : STD_LOGIC;

SIGNAL fftpts_in : STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL fftpts_out : STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL reset_n : STD_LOGIC;

SIGNAL sink_eop : STD_LOGIC;

SIGNAL sink_error : STD_LOGIC_VECTOR(1 DOWNTO 0);

SIGNAL sink_imag : STD_LOGIC_VECTOR(31 DOWNTO 0);

SIGNAL sink_ready : STD_LOGIC;

SIGNAL sink_real : STD_LOGIC_VECTOR(31 DOWNTO 0);

SIGNAL sink_sop : STD_LOGIC;

SIGNAL sink_valid : STD_LOGIC;

SIGNAL source_eop : STD_LOGIC;

SIGNAL source_error : STD_LOGIC_VECTOR(1 DOWNTO 0);

SIGNAL source_imag : STD_LOGIC_VECTOR(31 DOWNTO 0);

SIGNAL source_ready : STD_LOGIC;

SIGNAL source_real : STD_LOGIC_VECTOR(31 DOWNTO 0);

SIGNAL source_sop : STD_LOGIC;

SIGNAL source_valid : STD_LOGIC;

CONSTANT clk_period : TIME := 20 ns;

COMPONENT fft

PORT (

clk : IN STD_LOGIC;

fftpts_in : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

fftpts_out : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

reset_n : IN STD_LOGIC;

sink_eop : IN STD_LOGIC;

sink_error : IN STD_LOGIC_VECTOR(1 DOWNTO 0);

sink_imag : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

sink_ready : OUT STD_LOGIC;

sink_real : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

sink_sop : IN STD_LOGIC;

sink_valid : IN STD_LOGIC;

source_eop : OUT STD_LOGIC;

source_error : OUT STD_LOGIC_VECTOR(1 DOWNTO 0);

source_imag : OUT STD_LOGIC_VECTOR(31 DOWNTO 0);

source_ready : IN STD_LOGIC;

source_real : OUT STD_LOGIC_VECTOR(31 DOWNTO 0);

source_sop : OUT STD_LOGIC;

source_valid : OUT STD_LOGIC

);

END COMPONENT;

BEGIN

i1 : fft

PORT MAP (

-- list connections between master ports and signals

clk => clk,

fftpts_in => fftpts_in,

fftpts_out => fftpts_out,

reset_n => reset_n,

sink_eop => sink_eop,

sink_error => sink_error,

sink_imag => sink_imag,

sink_ready => sink_ready,

sink_real => sink_real,

sink_sop => sink_sop,

sink_valid => sink_valid,

source_eop => source_eop,

source_error => source_error,

source_imag => source_imag,

source_ready => source_ready,

source_real => source_real,

source_sop => source_sop,

source_valid => source_valid

);

init : PROCESS

-- variable declarations

BEGIN

sink_error<="00";

source_ready<='1';

fftpts_in<="1000";

reset_n<='1' ;

sink_valid<='1'; -- code that executes only once

WAIT;

END PROCESS init;

clk_generation:process

begin

clk<='1' ;

wait for clk_period/2;

clk<='0' ;

wait for clk_period/2;

end process;

always : PROCESS

-- optional sensitivity list

-- ( )

-- variable declarations

BEGIN

sink_imag<=(others=>'0');

sink_real<=(others=>'0'); -- code that executes only once

sink_eop<='0';

sink_sop<='0';

wait until rising_edge(clk);

wait until rising_edge(clk);

sink_sop<='1';

sink_real<="00000000010000000000000000000000";

sink_imag<="00000000010000000000000000000000";

wait until rising_edge(clk);

sink_sop<='0';

sink_real<="00000000011000000000000000000000";

sink_imag<="00000000011000000000000000000000";

wait until rising_edge(clk);

sink_real<="00000000011100000000000000000000";

sink_imag<="00000000011100000000000000000000";

wait until rising_edge(clk);

sink_real<="00000000011110000000000000000000";

sink_imag<="00000000011110000000000000000000";

wait until rising_edge(clk);

sink_real<="00000000011111000000000000000000";

sink_imag<="00000000011111000000000000000000";

wait until rising_edge(clk);

sink_real<="00000000011111100000000000000000";

sink_imag<="00000000011111100000000000000000";

wait until rising_edge(clk);

sink_real<="00000000011111110000000000000000";

sink_imag<="00000000011111110000000000000000";

wait until rising_edge(clk);

sink_eop<='1';

sink_real<="00000000011111111000000000000000";

sink_imag<="00000000011111111000000000000000";

wait until rising_edge(clk);

sink_eop<='0';

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

wait until rising_edge(clk);

-- code executes for every event on sensitivity list

WAIT;

END PROCESS always;

END fft_arch;

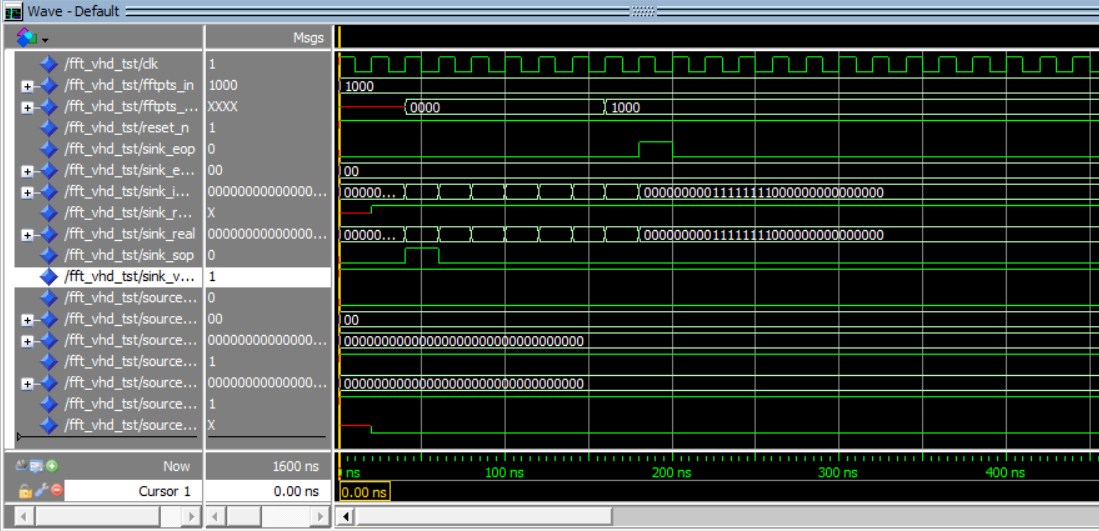

从输出的_fftpts_out 来看,ip核是能检测到了输入的。但是8个数据输入后输出并没有反应

ipcore是8数据,单浮点,可变流。

http://blog.csdn.net/wangming520liwei/article/details/27962617?locationNum=3