江湖告急:IMX6 串口引脚配置问题

项目中有用到imx6dl的UART2 以前的配置是:

MX6DL_PAD_EIM_D26__UART2_TXD,

MX6DL_PAD_EIM_D27__UART2_RXD,

经过测试能够正常收发

现在由于硬件RX与TX接反了 所以需要对调串口的配置在board-mx6dl_sabresd.h中修改引脚配置:

MX6DL_PAD_EIM_D26__UART2_RXD,

MX6DL_PAD_EIM_D27__UART2_TXD,

结果得不到理想的效果 (D26还是发送 D27不发也不收)

这个应该怎么配置呢 ? IMX6支持TX RX 对调吗

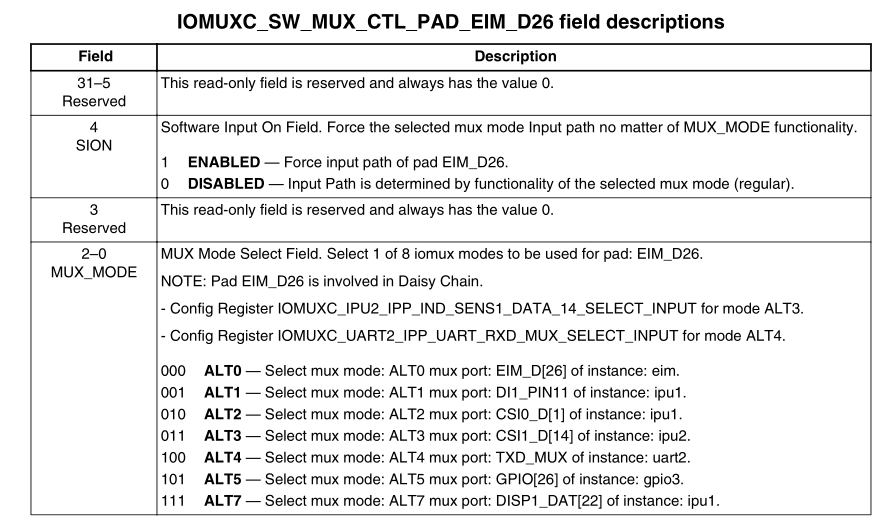

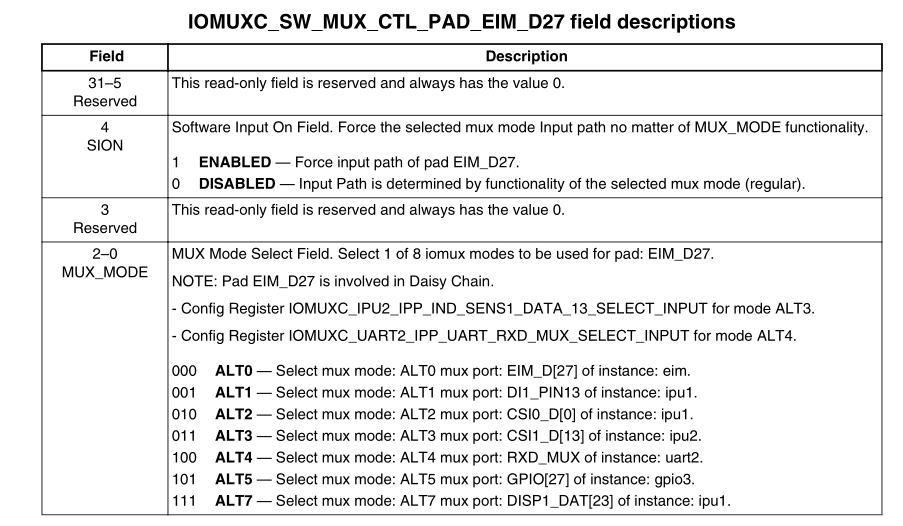

下面是官方的宏定义:

#define MX6DL_PAD_EIM_D26__UART2_TXD \

IOMUX_PAD(0x053C, 0x016C, 4, 0x0000, 0, MX6DL_UART_PAD_CTRL)

#define MX6DL_PAD_EIM_D26__UART2_RXD \

IOMUX_PAD(0x053C, 0x016C, 4, 0x0904, 0, MX6DL_UART_PAD_CTRL)

#define MX6DL_PAD_EIM_D27__UART2_TXD \

IOMUX_PAD(0x0540, 0x0170, 4, 0x0000, 0, MX6DL_UART_PAD_CTRL)

#define MX6DL_PAD_EIM_D27__UART2_RXD \

IOMUX_PAD(0x0540, 0x0170, 4, 0x0904, 1, MX6DL_UART_PAD_CTRL)

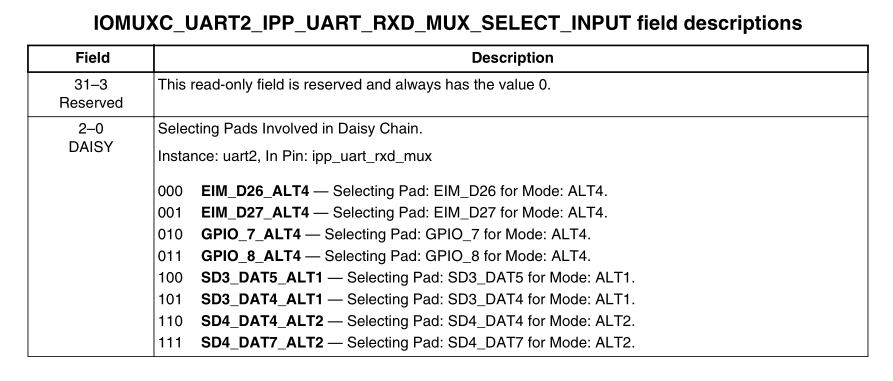

下面是相关寄存器:

imx6的板子上,想在原来基础上添加三个串口

你需要修改如下5个文件的内容,分别是board-mx6q_sabresd.h、board-mx6q_sabresd.c、platform-imx-uart.c、 clock.c、mx6.h修改如下:

1.board-mx6q_sabresd.h

/*UART2*/

MX6Q_PAD_EIM_D26_UART2_TXD,

MX6Q_PAD_EIM_D27_UART2_RXD,

/*UART4*/

MX6Q_PAD_KEY_COL0_UART4_RXD,

MX6Q_PAD_KEY_ROW0_UART4_TXD,

/*UART5 */

MX6Q_PAD_KEY_COL0_UART5_RXD,

MX6Q_PAD_KEY_ROW_UART5_TXD,

2.board-mx6q_sabresd.c

static inline void mx6q_sabresd_init_uart(void)

{

imx6q_add_imx_uart(0,NULL);

imx6q_add_imx_uart(1,NULL);

imx6q_add_imx_uart(2,NULL);

imx6q_add_imx_uart(3,NULL);

imx6q_add_imx_uart(4,NULL);

}

3.platform-imx-uart.c

#define imx6q_imx_uart_data_entry(_id, _hwid)

imx_imx_uart_lirq_data_entry(MX6Q, _id, _hwid, SZ_4K)

imx6q_imx_uart_data_entry(0,1),

imx6q_imx_uart_data_entry(1,2),

imx6q_imx_uart_data_entry(2,3),

imx6q_imx_uart_data_entry(3,4),

imx6q_imx_uart_data_entry(4,5),

};

4.clock.c

_REGISTER_CLOCK("imx_uart.0", NULL, uart_clk[0]),

_REGISTER_CLOCK("imx_uart.1", NULL, uart_clk[0]),

_REGISTER_CLOCK("imx_uart.2", NULL, uart_clk[0]),

_REGISTER_CLOCK("imx_uart.3", NULL, uart_clk[0]),

_REGISTER_CLOCK("imx_uart.4", NULL, uart_clk[0]),

5.mx6.h

#define MX6Q_UART1_BASE_ADDR UART1_BASE_ADDR

#define MX6Q_UART2_BASE_ADDR UART2_BASE_ADDR

#define MX6Q_UART3_BASE_ADDR UART3_BASE_ADDR

#define MX6Q_UART4_BASE_ADDR UART4_BASE_ADDR

#define MX6Q_UART5_BASE_ADDR UART5_BASE_ADDR

#define MX6Q_INT_UART1 MXC_INT_UART1_ANDED

#define MX6Q_INT_UART2 MXC_INT_UART2_ANDED

#define MX6Q_INT_UART3 MXC_INT_UART3_ANDED

#define MX6Q_INT_UART4 MXC_INT_UART4_ANDED

#define MX6Q_INT_UART5 MXC_INT_UART5_ANDED

图片发错了 不是imxdl的寄存器 除了地址其他都一样