哪位大神熟悉FPGA的FIFO操作,尤其是IP软核,帮个忙分析一下原因

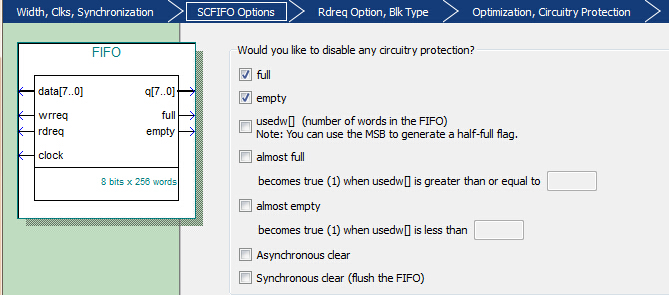

这是我用IP核生成的FIFO,测试了一下,为什么q[7:0]输出的数据全都是00啊?顶层中重实例化的FIFO:

FIFO FIFO_inst(

.clock ( clk ),

.data ( Rx_Data ),

.rdreq ( read ),

.wrreq (write),

.empty ( empty_sig ),

.full ( full_sig ),

.q ( Tx_Data )

);

串行接收数据时write=1, read =0,另外两两数据之间有个空闲时间,这时write=0, read =1,就这样交替着读写,请问有哪里错了吗?

http://www.cnblogs.com/BitArt/archive/2013/04/10/3010073.html

full和empty指示FIFO里面有没有数据,clk打拍,wt有效,data就存入FIFO,rd有效,FIFO数据就挂Q上,“交替着读写”,没有数据你读啥,或者读比写快你读啥,full和empty要用的。

FIFO的关键就在于full和empty两个信号的判断,非空时才能读数据,没满时才能写数据