这是一个关于计算机组成原理的相关问题

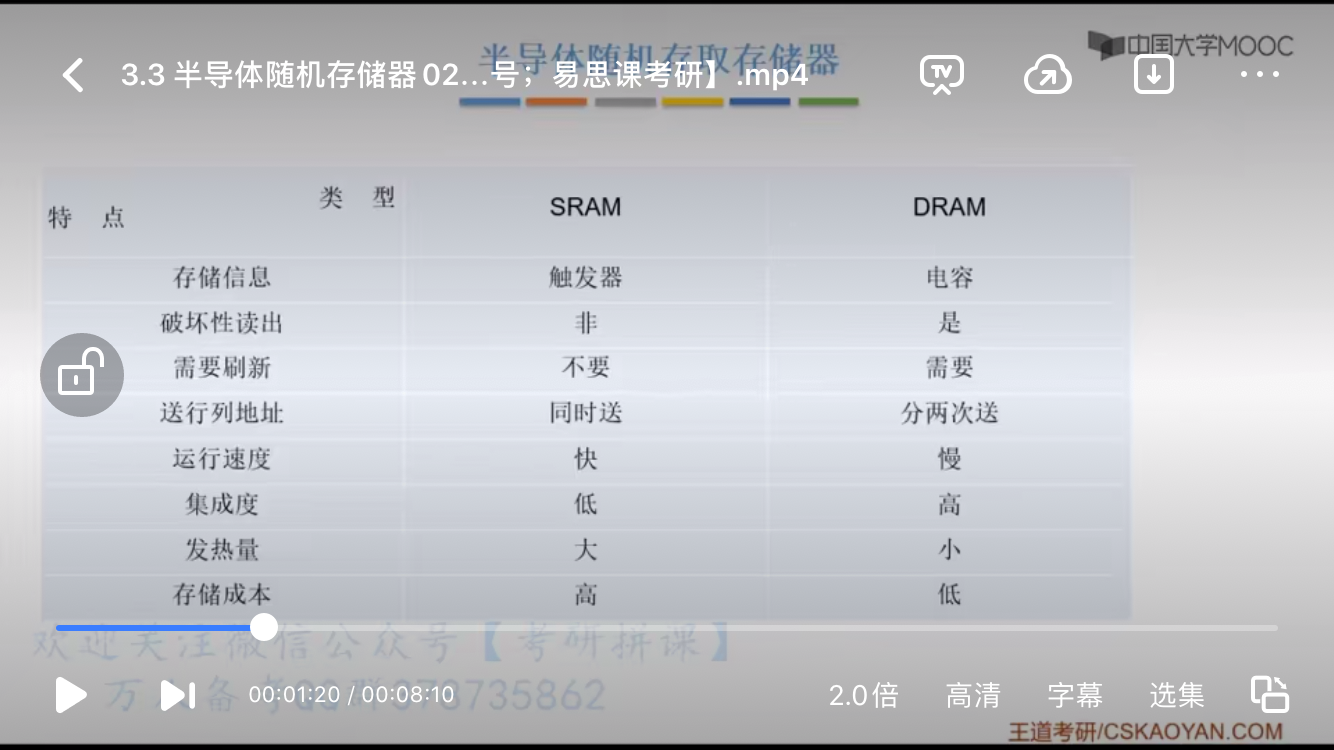

如图,请问送行列地址,为啥SRAM为一次,DRAM为两次?

为啥SRAM需要破坏性读出,DRAM不需要?

还有发热情况,大小咋出来的?

这些都是元器件的物理特性决定的。分两次主要是为了节约地址线

SRAM使用由多个MOS管组成的触发器存储信息,6个MOS管共同组成一个基本单元,即6个MOS管存储1位二进制信息。由于它使用触发器工作原理存储信息,因此即使信息读出后,仍然保持其原状态(即二进制信息不变),不需要再生。其基本单元包含的元件很多(6个)所以每个单位面积发热较大,集成度低,存储成本高。

DRAM使用电容存储电荷的原理存储信息,由于电容电荷的易失性,一般必须在2ms内对其所有存储单元进行一次刷新(对里面的电荷进行恢复), DRAM的存储单元由1个晶体管和一个电容组成,基本单元中元件较少,所以其集成度较高,发热量小,存储成本低。

至于为何送地址时SRAM为1次,而DRAM为两次,当然是由于其地址线条数不同,SRAM由于其速度快价格高集成度低不需要刷新等特点,主要用于高速Cache,对速度的要求使其设计牺牲集成度(更多的地址线需要更多的引脚会使其体积变大)来获得更快的存取速度,而DRAM由于其位价低等特点主要用于内存,对速度的要求低于对集成度的要求,所以使用较少的地址线分两次传输地址。

关于是否破坏性读出这一点,也是由于电容的易失性导致的。