关于FPGA位宽问题 verilog语言 相乘怎么处理

这道题怎么解决 信号相乘是怎么处理

verilog语言

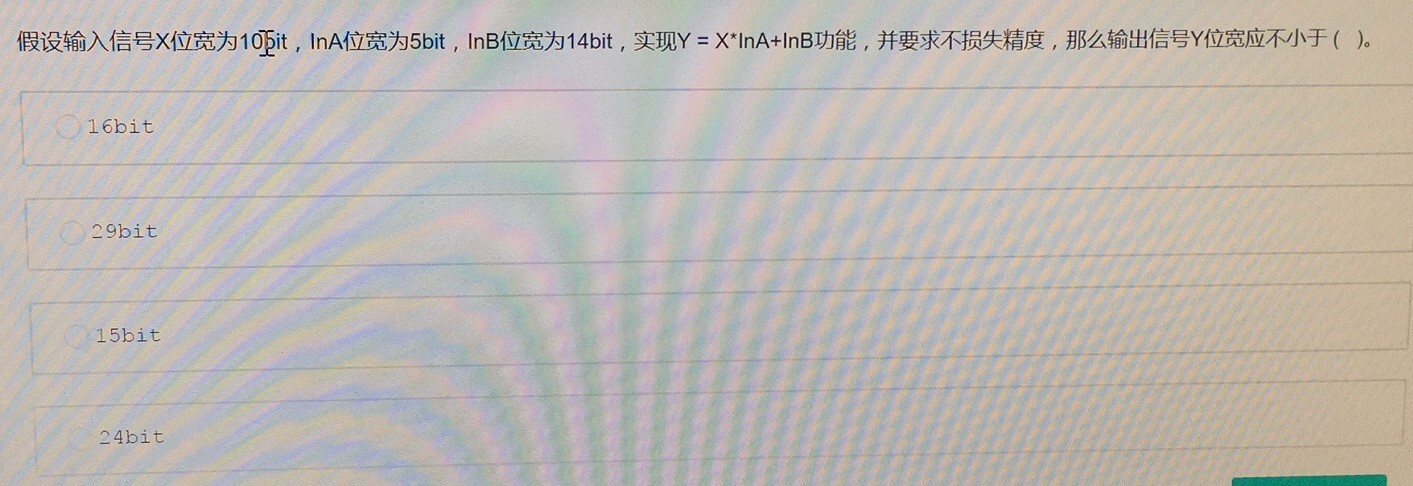

16bit吧, 两数相乘10bit+5bit = 15bit, 然后加上一个14bit数,考虑到溢出,所以16bit

两数相乘,位宽相加;

两数相加,位宽加一;

至少16bit;

好家伙,华为笔试吗这不是

16bit, 但不是所有情况都达到16bit,如果改变数值你会发现有些情况下是15bit

“乘法:位宽相加;加法位宽加1”原则是针对所有状况的,当处理具体数句时可以根据实际数据范围来确定最大位宽,即算出最大值,用该值的位宽就可以了

原则:位宽取最大可能值

规则:两数相乘,结果位宽为两乘数位宽的和;两数相加,结果位宽为加数中位宽最大的加数的位宽加一。

直接上答案:10+5+1=16

16bit